15-24 Vol. 3B

MACHINE-CHECK ARCHITECTURE

For both the memory scrubbing and L3 explicit writeback errors, the ADDRV and MISCV flags in the

IA32_MCi_STATUS register are set to indicate that the offending physical address information is available from the

IA32_MCi_MISC and the IA32_MCi_ADDR registers. For the memory scrubbing and L3 explicit writeback errors,

the address mode in the IA32_MCi_MISC register should be set as physical address mode (010b) and the address

LSB information in the IA32_MCi_MISC register should indicate the lowest valid address bit in the address informa-

tion provided from the IA32_MCi_ADDR register.

MCE signal is broadcast to all logical processors as outlined in Section 15.10.4.1. If LMCE is supported and enabled,

some errors (not limited to UCR errors) may be delivered to only a single logical processor. System software should

consult IA32_MCG_STATUS.LMCE_S to determine if the MCE signaled is only to this logical processor.

IA32_MCi_STATUS banks can be shared by logical processors within a core or within the same package. So several

logical processors may find an SRAO error in the shared IA32_MCi_STATUS bank but other processors do not find

it in any of the IA32_MCi_STATUS banks. Table 15-17 shows the RIPV and EIPV flag indication in the

IA32_MCG_STATUS register for the memory scrubbing and L3 explicit writeback errors on both the reporting and

non-reporting logical processors.

15.9.3.2 Architecturally Defined SRAR Errors

The following two SRAR errors are architecturally defined.

•

UCR Errors detected on data load; and

•

UCR Errors detected on instruction fetch.

The MCA error code encodings for these two architecturally-defined UCR errors corresponds to sub-classes of

compound MCA error codes (see Table 15-9). Their values and compound encoding format are given in Table

15-18.

NOTES:

1. When signaled as MCE, EN=1 and S=1. If error was signaled via CMC, then EN=x, and S=0.

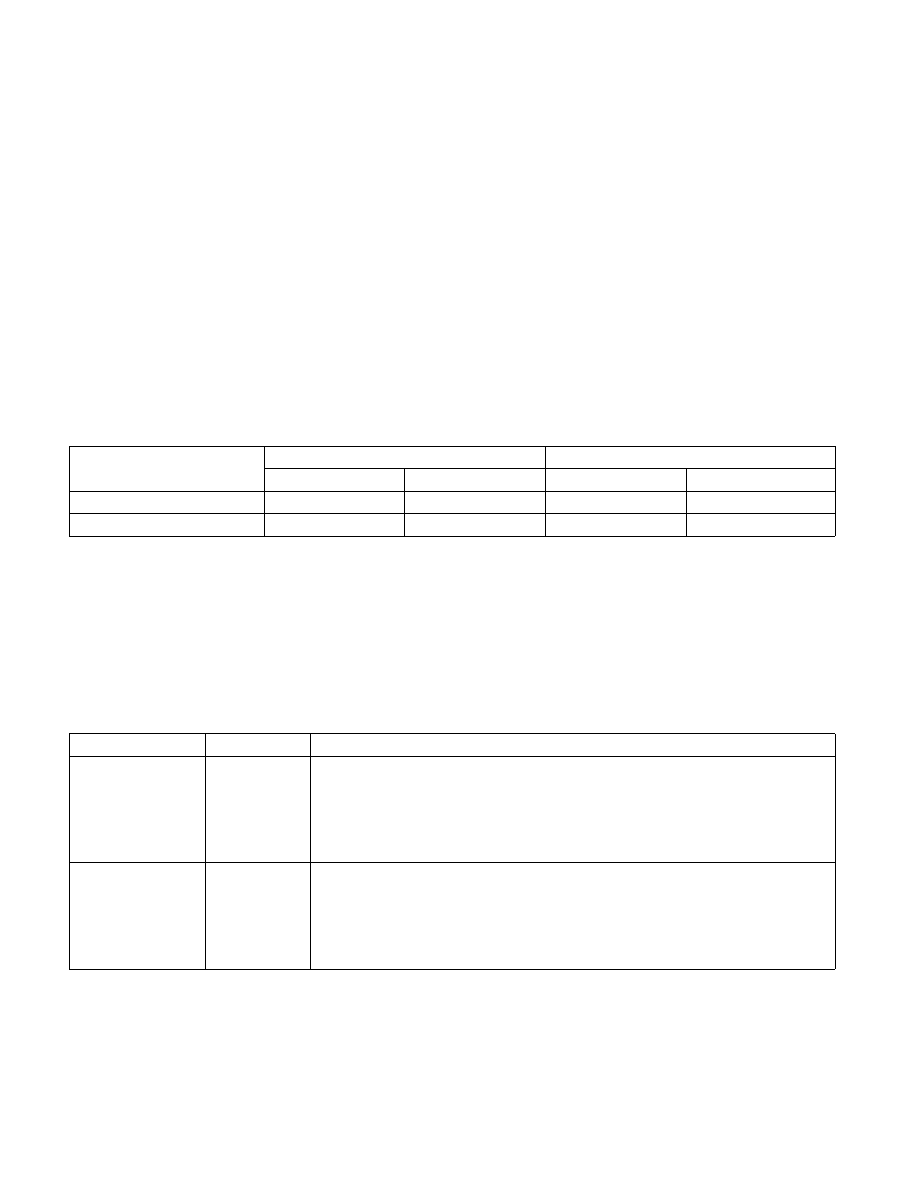

Table 15-17. IA32_MCG_STATUS Flag Indication for SRAO Errors

SRAO Type

Reporting Logical Processors

Non-reporting Logical Processors

RIPV

EIPV

RIPV

EIPV

Memory Scrubbing

1

0

1

0

L3 Explicit Writeback

1

0

1

0

Table 15-18. MCA Compound Error Code Encoding for SRAR Errors

Type

MCACOD Value MCA Error Code Encoding

1

NOTES:

1. Note that for both of these errors the correction report filtering (F) bit (bit 12) of the MCA error must be ignored.

Data Load

134H

0000_0001_0011_0100

000F 0001 RRRR TTLL (Cache Hierarchy Error), where

Request subfield RRRR = 0011B (Data Load)

Transaction Type subfield TT= 01B (Data)

Level subfield LL = 00B (Level 0)

Instruction Fetch

150H

0000_0001_0101_0000

000F 0001 RRRR TTLL (Cache Hierarchy Error), where

Request subfield RRRR = 0101B (Instruction Fetch)

Transaction Type subfield TT= 00B (Instruction)

Level subfield LL = 00B (Level 0)