10-6 Vol. 3A

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

FP/MMX/SSE access to an APIC register, or any access that touches bytes 4 through 15 of an APIC register may

cause undefined behavior and must not be executed. This undefined behavior could include hangs, incorrect results

or unexpected exceptions, including machine checks, and may vary between implementations. Wider registers

(64-bit or 256-bit) must be accessed using multiple 32-bit loads or stores, with all accesses being 128-bit aligned.

The local APIC registers listed in Table 10-1 are not MSRs. The only MSR associated with the programming of the

local APIC is the IA32_APIC_BASE MSR (see Section 10.4.3, “Enabling or Disabling the Local APIC”).

NOTE

In processors based on Intel microarchitecture code name Nehalem the Local APIC ID Register is no

longer Read/Write; it is Read Only.

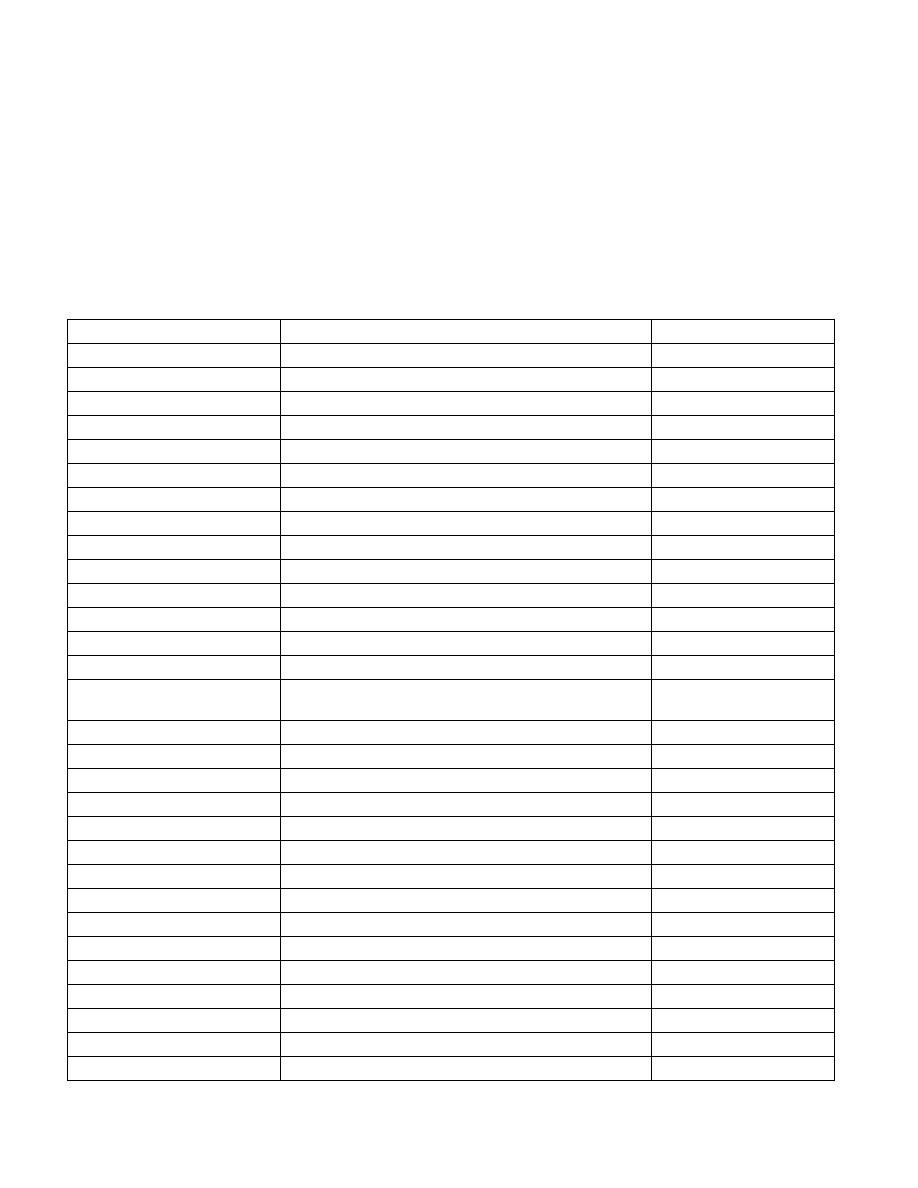

Table 10-1 Local APIC Register Address Map

Address

Register Name

Software Read/Write

FEE0 0000H

Reserved

FEE0 0010H

Reserved

FEE0 0020H

Local APIC ID Register

Read/Write.

FEE0 0030H

Local APIC Version Register

Read Only.

FEE0 0040H

Reserved

FEE0 0050H

Reserved

FEE0 0060H

Reserved

FEE0 0070H

Reserved

FEE0 0080H

Task Priority Register (TPR)

Read/Write.

FEE0 0090H

Arbitration Priority Register

1

(APR)

Read Only.

FEE0 00A0H

Processor Priority Register (PPR)

Read Only.

FEE0 00B0H

EOI Register

Write Only.

FEE0 00C0H

Remote Read Register

1

(RRD)

Read Only

FEE0 00D0H

Logical Destination Register

Read/Write.

FEE0 00E0H

Destination Format Register

Read/Write (see Section

FEE0 00F0H

Spurious Interrupt Vector Register

Read/Write (see Section 10.9.

FEE0 0100H

In-Service Register (ISR); bits 31:0

Read Only.

FEE0 0110H

In-Service Register (ISR); bits 63:32

Read Only.

FEE0 0120H

In-Service Register (ISR); bits 95:64

Read Only.

FEE0 0130H

In-Service Register (ISR); bits 127:96

Read Only.

FEE0 0140H

In-Service Register (ISR); bits 159:128

Read Only.

FEE0 0150H

In-Service Register (ISR); bits 191:160

Read Only.

FEE0 0160H

In-Service Register (ISR); bits 223:192

Read Only.

FEE0 0170H

In-Service Register (ISR); bits 255:224

Read Only.

FEE0 0180H

Trigger Mode Register (TMR); bits 31:0

Read Only.

FEE0 0190H

Trigger Mode Register (TMR); bits 63:32

Read Only.

FEE0 01A0H

Trigger Mode Register (TMR); bits 95:64

Read Only.

FEE0 01B0H

Trigger Mode Register (TMR); bits 127:96

Read Only.

FEE0 01C0H

Trigger Mode Register (TMR); bits 159:128

Read Only.

FEE0 01D0H

Trigger Mode Register (TMR); bits 191:160

Read Only.