15-10 Vol. 3B

MACHINE-CHECK ARCHITECTURE

•

Recoverable Address LSB (bits 5:0): The lowest valid recoverable address bit. Indicates the position of the least

significant bit (LSB) of the recoverable error address. For example, if the processor logs bits [43:9] of the

address, the LSB sub-field in IA32_MCi_MISC is 01001b (9 decimal). For this example, bits [8:0] of the

recoverable error address in IA32_MCi_ADDR should be ignored.

•

Address Mode (bits 8:6): Address mode for the address logged in IA32_MCi_ADDR. The supported address

modes are given in Table 15-3.

•

Model Specific Information (bits 63:9): Not architecturally defined.

15.3.2.5 IA32_MC

i

_CTL2 MSRs

The IA32_MCi_CTL2 MSR provides the programming interface to use corrected MC error signaling capability that is

indicated by IA32_MCG_CAP[10] = 1. Software must check for the presence of IA32_MCi_CTL2 on a per-bank

basis.

When IA32_MCG_CAP[10] = 1, the IA32_MCi_CTL2 MSR for each bank exists, i.e. reads and writes to these MSR

are supported. However, signaling interface for corrected MC errors may not be supported in all banks.

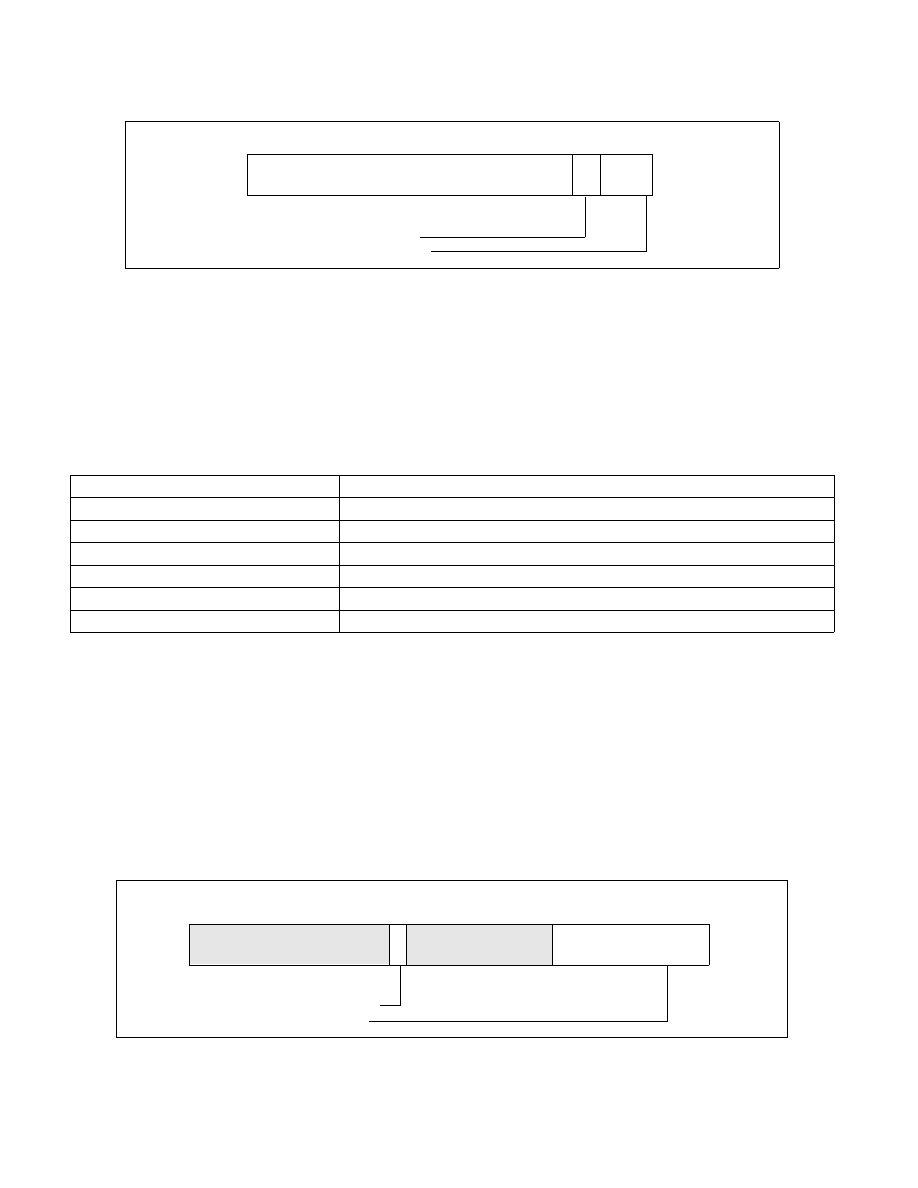

The layout of IA32_MCi_CTL2 is shown in Figure 15-9:

Figure 15-8. UCR Support in IA32_MCi_MISC Register

Table 15-3. Address Mode in IA32_MCi_MISC[8:6]

IA32_MCi_MISC[8:6] Encoding

Definition

000

Segment Offset

001

Linear Address

010

Physical Address

011

Memory Address

100 to 110

Reserved

111

Generic

Figure 15-9. IA32_MCi_CTL2 Register

Address Mode

63

0

Model Specific Information

6 5

Recoverable Address LSB

8

9

CMCI_EN—Enable/disable CMCI

63

15

Reserved

29

Corrected error count threshold

0

14

31 30

Reserved