15-8 Vol. 3B

MACHINE-CHECK ARCHITECTURE

•

PCC (processor context corrupt) flag, bit 57 — Indicates (when set) that the state of the processor might

have been corrupted by the error condition detected and that reliable restarting of the processor may not be

possible. When clear, this flag indicates that the error did not affect the processor’s state, and software may be

able to restart. When system software supports recovery, consult Section 15.10.4, “Machine-Check Software

Handler Guidelines for Error Recovery” for additional rules that apply.

•

ADDRV (IA32_MCi_ADDR register valid) flag, bit 58 — Indicates (when set) that the IA32_MCi_ADDR

register contains the address where the error occurred (see Section 15.3.2.3, “IA32_MCi_ADDR MSRs”). When

clear, this flag indicates that the IA32_MCi_ADDR register is either not implemented or does not contain the

address where the error occurred. Do not read these registers if they are not implemented in the processor.

•

MISCV (IA32_MCi_MISC register valid) flag, bit 59 — Indicates (when set) that the IA32_MCi_MISC

register contains additional information regarding the error. When clear, this flag indicates that the

IA32_MCi_MISC register is either not implemented or does not contain additional information regarding the

error. Do not read these registers if they are not implemented in the processor.

•

EN (error enabled) flag, bit 60 — Indicates (when set) that the error was enabled by the associated EEj bit

of the IA32_MCi_CTL register.

•

UC (error uncorrected) flag, bit 61 — Indicates (when set) that the processor did not or was not able to

correct the error condition. When clear, this flag indicates that the processor was able to correct the error

condition.

•

OVER (machine check overflow) flag, bit 62 — Indicates (when set) that a machine-check error occurred

while the results of a previous error were still in the error-reporting register bank (that is, the VAL bit was

already set in the IA32_MCi_STATUS register). The processor sets the OVER flag and software is responsible for

clearing it. In general, enabled errors are written over disabled errors, and uncorrected errors are written over

corrected errors. Uncorrected errors are not written over previous valid uncorrected errors. When

MCG_CMCI_P is set, corrected errors may not set the OVER flag. Software can rely on corrected error count in

IA32_MCi_Status[52:38] to determine if any additional corrected errors may have occurred. For more infor-

mation, see Section 15.3.2.2.1, “Overwrite Rules for Machine Check Overflow”.

•

VAL (IA32_MCi_STATUS register valid) flag, bit 63 — Indicates (when set) that the information within the

IA32_MCi_STATUS register is valid. When this flag is set, the processor follows the rules given for the OVER flag

in the IA32_MCi_STATUS register when overwriting previously valid entries. The processor sets the VAL flag

and software is responsible for clearing it.

15.3.2.2.1 Overwrite Rules for Machine Check Overflow

Table 15-2 shows the overwrite rules for how to treat a second event if the cache has already posted an event to

the MC bank – that is, what to do if the valid bit for an MC bank already is set to 1. When more than one structure

posts events in a given bank, these rules specify whether a new event will overwrite a previous posting or not.

These rules define a priority for uncorrected (highest priority), yellow, and green/unmonitored (lowest priority)

status.

In Table 15-2, the values in the two left-most columns are IA32_MCi_STATUS[54:53].

If a second event overwrites a previously posted event, the information (as guarded by individual valid bits) in the

MCi bank is entirely from the second event. Similarly, if a first event is retained, all of the information previously

posted for that event is retained. In general, when the logged error or the recent error is a corrected error, the

OVER bit (MCi_Status[62]) may be set to indicate an overflow. When MCG_CMCI_P is set in IA32_MCG_CAP,

system software should consult IA32_MCi_STATUS[52:38] to determine if additional corrected errors may have

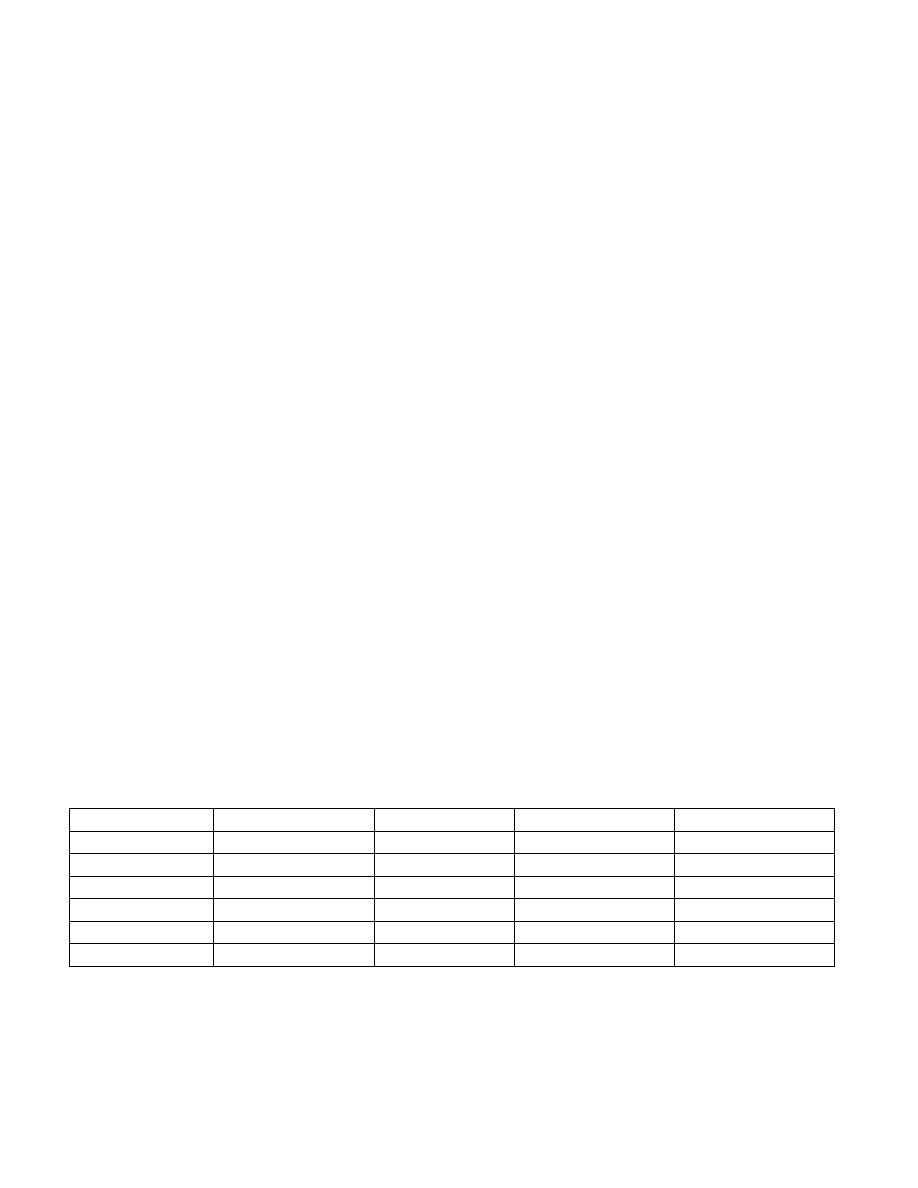

Table 15-2. Overwrite Rules for Enabled Errors

First Event

Second Event

UC bit

Color

MCA Info

00/green

00/green

0

00/green

either

00/green

yellow

0

yellow

second error

yellow

00/green

0

yellow

first error

yellow

yellow

0

yellow

either

00/green/yellow

UC

1

undefined

second

UC

00/green/yellow

1

undefined

first