14-28 Vol. 3B

POWER AND THERMAL MANAGEMENT

14.7.6

Power Limit Notification

Platform firmware may be capable of specifying a power limit to restrict power delivered to a platform component,

such as a physical processor package. This constraint imposed by platform firmware may occasionally cause the

processor to operate below OS-requested P or T-state. A power limit notification event can be delivered using the

existing thermal LVT entry in the local APIC.

Software can enumerate the presence of the processor’s support for power limit notification by verifying

CPUID.06H:EAX[bit 4] = 1.

If CPUID.06H:EAX[bit 4] = 1, then IA32_THERM_INTERRUPT and IA32_THERM_STATUS provides the following

facility to manage power limit notification:

•

Bits 10 and 11 in IA32_THERM_STATUS informs software of the occurrence of processor operating below OS-

requested P-state or clock modulation duty cycle setting (see Figure 14-27).

•

Bit 24 in IA32_THERM_INTERRUPT enables the local APIC to deliver a thermal event when the processor went

below OS-requested P-state or clock modulation duty cycle setting (see Figure 14-28).

14.8

PACKAGE LEVEL THERMAL MANAGEMENT

The thermal management facilities like IA32_THERM_INTERRUPT and IA32_THERM_STATUS are often imple-

mented with a processor core granularity. To facilitate software manage thermal events from a package level gran-

ularity, two architectural MSR is provided for package level thermal management. The

IA32_PACKAGE_THERM_STATUS and IA32_PACKAGE_THERM_INTERRUPT MSRs use similar interfaces as

IA32_THERM_STATUS and IA32_THERM_INTERRUPT, but are shared in each physical processor package.

Software can enumerate the presence of the processor’s support for package level thermal management facility

(IA32_PACKAGE_THERM_STATUS and IA32_PACKAGE_THERM_INTERRUPT) by verifying CPUID.06H:EAX[bit 6] =

1.

The layout of IA32_PACKAGE_THERM_STATUS MSR is shown in Figure 14-29.

•

Package Thermal Status (bit 0, RO) — This bit indicates whether the digital thermal sensor high-

temperature output signal (PROCHOT#) for the package is currently active. Bit 0 = 1 indicates the feature is

active. This bit may not be written by software; it reflects the state of the digital thermal sensor.

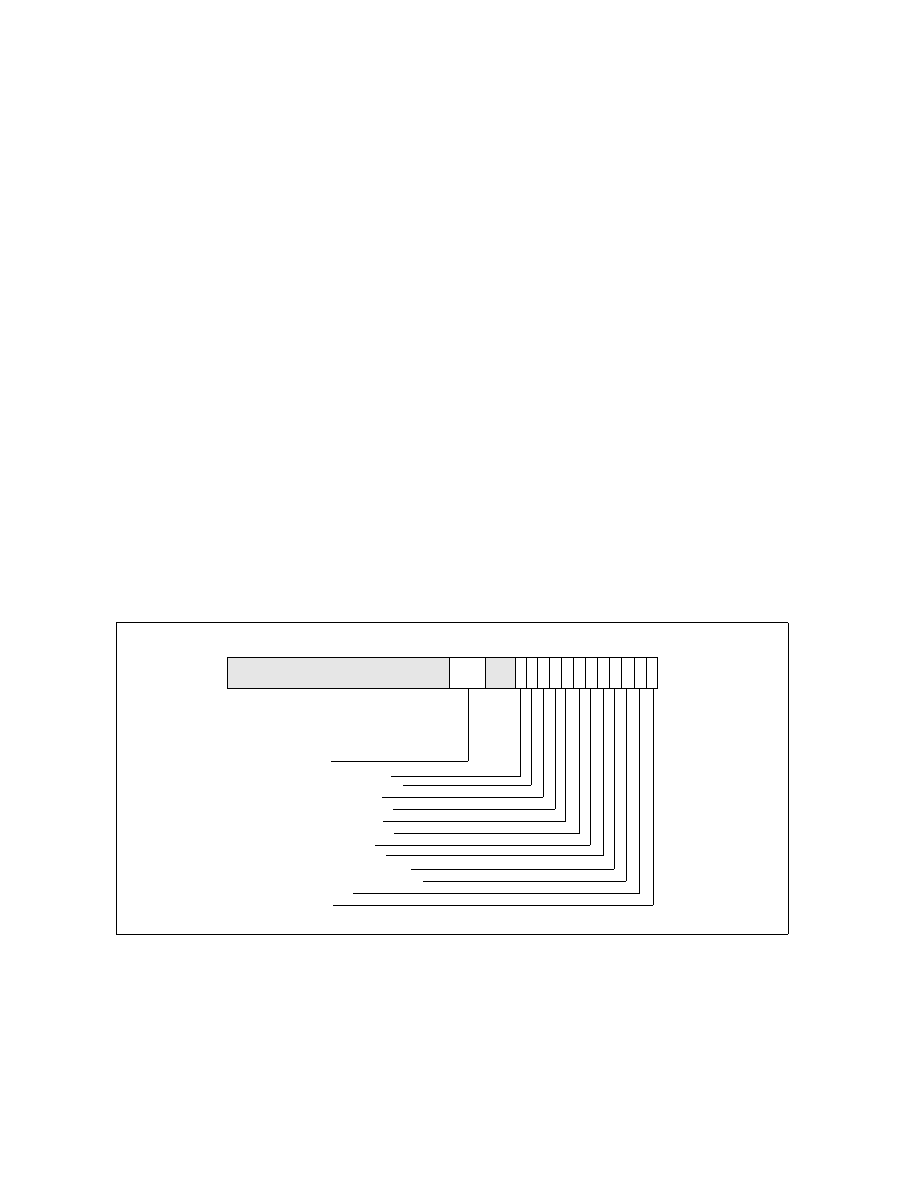

Figure 14-29. IA32_PACKAGE_THERM_STATUS Register

63

0

Reserved

15

1

2

3

4

5

8

10

16

22

23

27

PKG Digital Readout

PKG Thermal Threshold #2 Log

PKG Thermal Threshold #2 Status

PKG Thermal Threshold #1 Log

PKG Thermal Threshold #1 Status

PKG Critical Temperature Log

6

7

9

31

32

PKG Critical Temperature Status

PKG PROCHOT# or FORCEPR# Log

PKG PROCHOT# or FORCEPR# Event

PKG Thermal Status Log

PKG Thermal Status

11

PKG Power Limit Notification Log

PKG Power Limit Notification Status