Vol. 3A 11-15

MEMORY CACHE CONTROL

2. If the PCD flag is set, then the effective memory type is UC.

3. If the PCD flag is clear and the PWT flag is set, the effective memory type is WT for the WB memory type and

the MTRR-defined memory type for all other memory types.

4. Setting the PCD and PWT flags to opposite values is considered model-specific for the WP and WC memory

types and architecturally-defined for the WB, WT, and UC memory types.

11.5.2.2 Selecting Memory Types for Pentium III and More Recent Processor Families

The Intel Core 2 Duo, Intel Atom, Intel Core Duo, Intel Core Solo, Pentium M, Pentium 4, Intel Xeon, and Pentium

III

processors use the PAT to select effective page-level memory types. Here, a memory type for a page is selected

by the MTRRs and the value in a PAT entry that is selected with the PAT, PCD and PWT bits in a page-table or page-

directory entry (see Section 11.12.3, “Selecting a Memory Type from the PAT”). Table 11-7 describes the mapping

of MTRR memory types and PAT entry types to effective memory types, when normal caching is in effect (the CD

and NW flags in control register CR0 are clear).

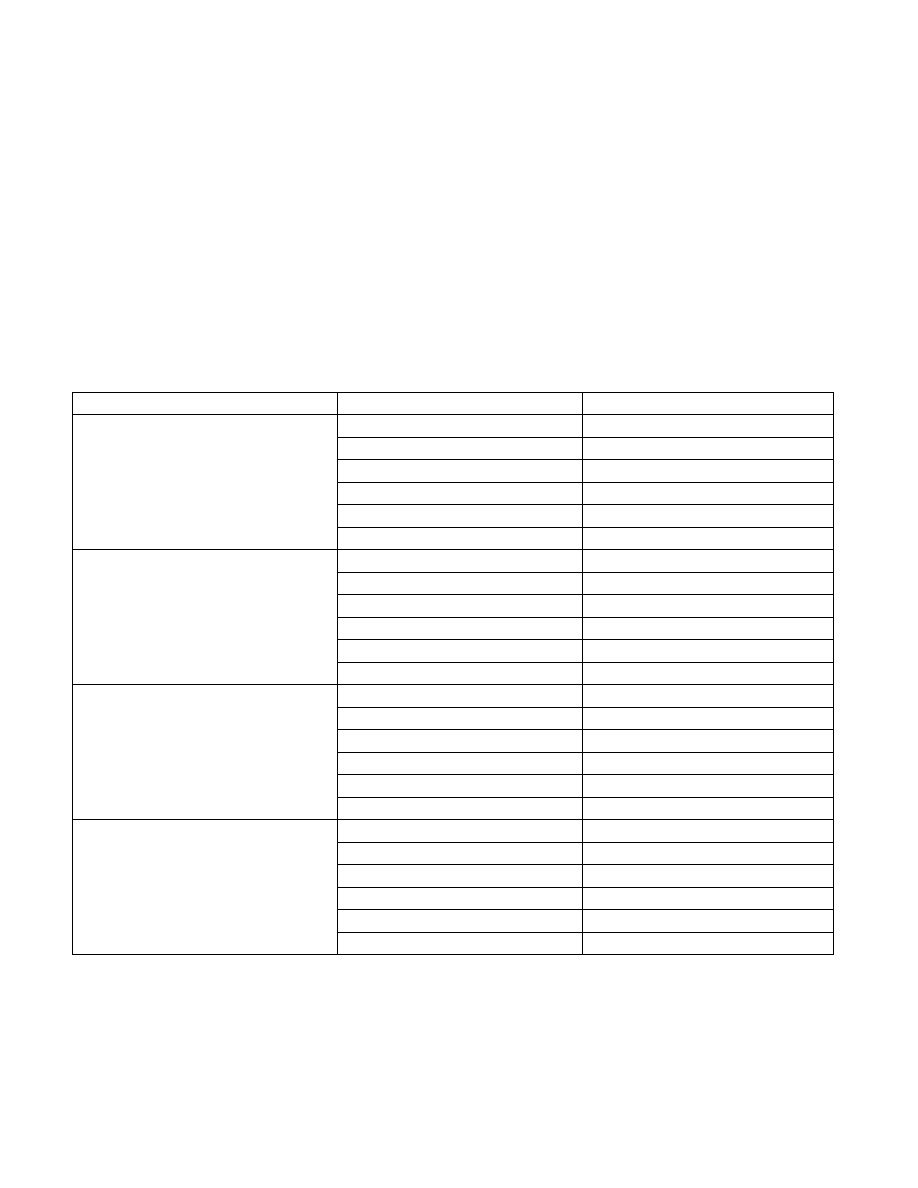

Table 11-7. Effective Page-Level Memory Types for Pentium III and More Recent Processor Families

MTRR Memory Type

PAT Entry Value

Effective Memory Type

UC UC

UC

1

UC-

UC

1

WC

WC

WT

UC

1

WB

UC

1

WP

UC

1

WC

UC

UC

2

UC-

WC

WC

WC

WT

UC

2,3

WB

WC

WP

UC

2,3

WT

UC

UC

2

UC-

UC

2

WC

WC

WT

WT

WB

WT

WP

WP

3

WB

UC

UC

2

UC-

UC

2

WC

WC

WT

WT

WB

WB

WP

WP