Vol. 3A 11-7

MEMORY CACHE CONTROL

•

Write Combining (WC) — System memory locations are not cached (as with uncacheable memory) and

coherency is not enforced by the processor’s bus coherency protocol. Speculative reads are allowed. Writes

may be delayed and combined in the write combining buffer (WC buffer) to reduce memory accesses. If the WC

buffer is partially filled, the writes may be delayed until the next occurrence of a serializing event; such as, an

SFENCE or MFENCE instruction, CPUID execution, a read or write to uncached memory, an interrupt

occurrence, or a LOCK instruction execution. This type of cache-control is appropriate for video frame buffers,

where the order of writes is unimportant as long as the writes update memory so they can be seen on the

graphics display. See Section 11.3.1, “Buffering of Write Combining Memory Locations,” for more information

about caching the WC memory type. This memory type is available in the Pentium Pro and Pentium II

processors by programming the MTRRs; or in processor families starting from the Pentium III processors by

programming the MTRRs or by selecting it through the PAT.

•

Write-through (WT) — Writes and reads to and from system memory are cached. Reads come from cache

lines on cache hits; read misses cause cache fills. Speculative reads are allowed. All writes are written to a

cache line (when possible) and through to system memory. When writing through to memory, invalid cache

lines are never filled, and valid cache lines are either filled or invalidated. Write combining is allowed. This type

of cache-control is appropriate for frame buffers or when there are devices on the system bus that access

system memory, but do not perform snooping of memory accesses. It enforces coherency between caches in

the processors and system memory.

•

Write-back (WB) — Writes and reads to and from system memory are cached. Reads come from cache lines

on cache hits; read misses cause cache fills. Speculative reads are allowed. Write misses cause cache line fills

(in processor families starting with the P6 family processors), and writes are performed entirely in the cache,

when possible. Write combining is allowed. The write-back memory type reduces bus traffic by eliminating

many unnecessary writes to system memory. Writes to a cache line are not immediately forwarded to system

memory; instead, they are accumulated in the cache. The modified cache lines are written to system memory

later, when a write-back operation is performed. Write-back operations are triggered when cache lines need to

be deallocated, such as when new cache lines are being allocated in a cache that is already full. They also are

triggered by the mechanisms used to maintain cache consistency. This type of cache-control provides the best

performance, but it requires that all devices that access system memory on the system bus be able to snoop

memory accesses to insure system memory and cache coherency.

•

Write protected (WP) — Reads come from cache lines when possible, and read misses cause cache fills.

Writes are propagated to the system bus and cause corresponding cache lines on all processors on the bus to

be invalidated. Speculative reads are allowed. This memory type is available in processor families starting from

the P6 family processors by programming the MTRRs (see Table 11-6).

Table 11-3 shows which of these caching methods are available in the Pentium, P6 Family, Pentium 4, and Intel

Xeon processors.

11.3.1

Buffering of Write Combining Memory Locations

Writes to the WC memory type are not cached in the typical sense of the word cached. They are retained in an

internal write combining buffer (WC buffer) that is separate from the internal L1, L2, and L3 caches and the store

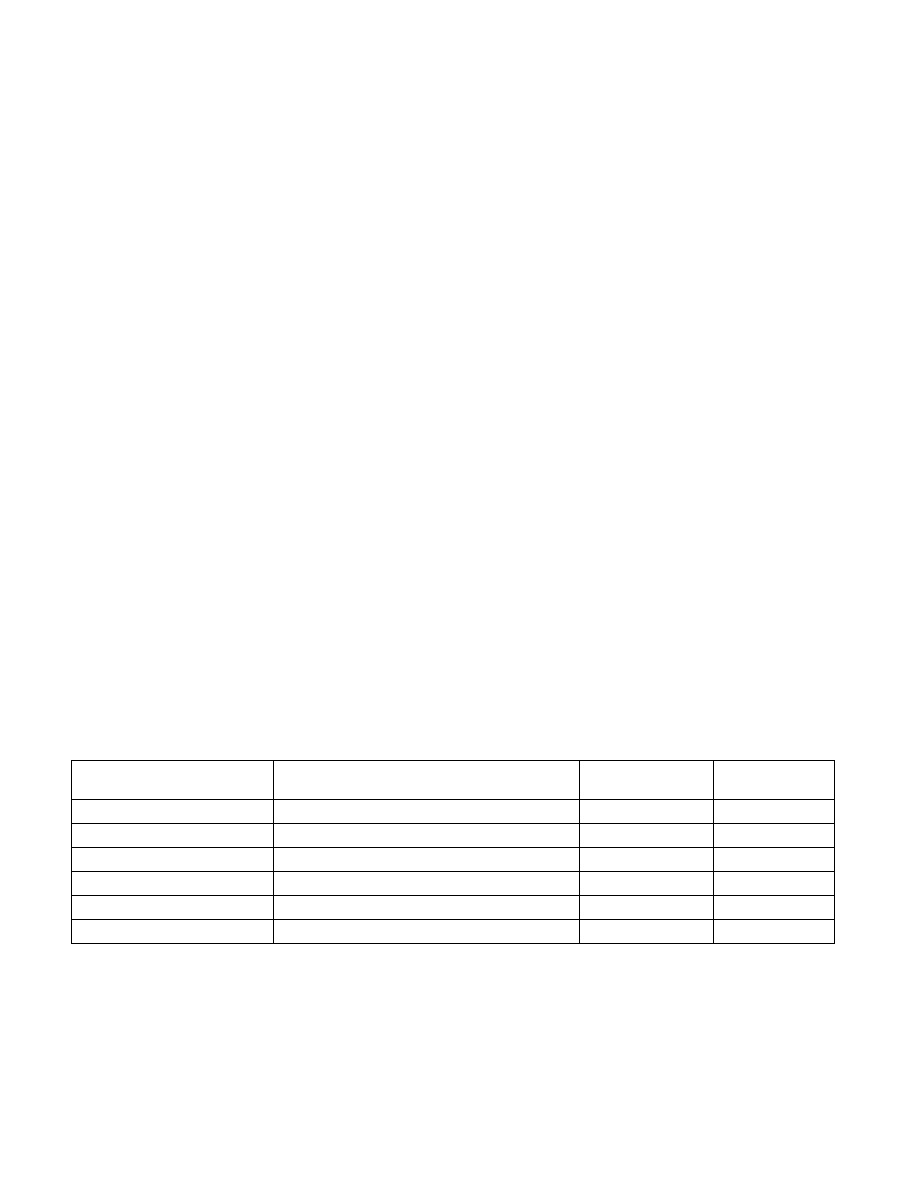

Table 11-3. Methods of Caching Available in Intel Core 2 Duo, Intel Atom, Intel Core Duo, Pentium M, Pentium 4,

Intel Xeon, P6 Family, and Pentium Processors

Memory Type

Intel Core 2 Duo, Intel Atom, Intel Core Duo,

Pentium M, Pentium 4 and Intel Xeon Processors

P6 Family

Processors

Pentium

Processor

Strong Uncacheable (UC)

Yes

Yes

Yes

Uncacheable (UC-)

Yes

Yes*

No

Write Combining (WC)

Yes

Yes

No

Write Through (WT)

Yes

Yes

Yes

Write Back (WB)

Yes

Yes

Yes

Write Protected (WP)

Yes

Yes

No

NOTE:

* Introduced in the Pentium III processor; not available in the Pentium Pro or Pentium II processors