11-14 Vol. 3A

MEMORY CACHE CONTROL

true; that is, if a page-level caching control designates a page as uncacheable, an MTRR cannot be used to make

the page cacheable.

In cases where there is a overlap in the assignment of the write-back and write-through caching policies to a page

and a region of memory, the write-through policy takes precedence. The write-combining policy (which can only be

assigned through an MTRR or the PAT) takes precedence over either write-through or write-back.

The selection of memory types at the page level varies depending on whether PAT is being used to select memory

types for pages, as described in the following sections.

On processors based on Intel NetBurst microarchitecture, the third-level cache can be disabled by bit 6 of the

IA32_MISC_ENABLE MSR. Using IA32_MISC_ENABLE[bit 6] takes precedence over the CD flag, MTRRs, and PAT

for the L3 cache in those processors. That is, when the third-level cache disable flag is set (cache disabled), the

other cache controls have no affect on the L3 cache; when the flag is clear (enabled), the cache controls have the

same affect on the L3 cache as they have on the L1 and L2 caches.

IA32_MISC_ENABLE[bit 6] is not supported in Intel Core i7 processors, nor processors based on Intel Core, and

Intel Atom microarchitectures.

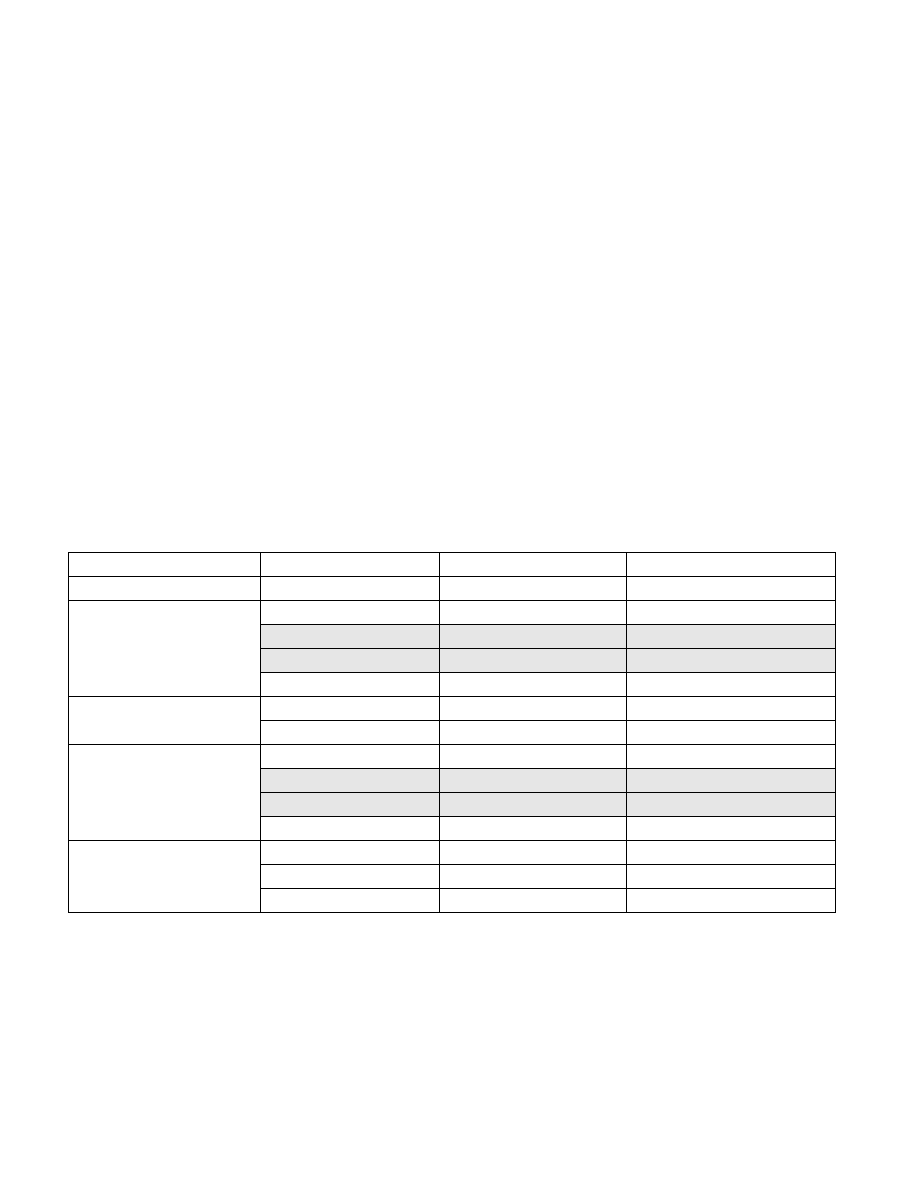

11.5.2.1 Selecting Memory Types for Pentium Pro and Pentium II Processors

The Pentium Pro and Pentium II processors do not support the PAT. Here, the effective memory type for a page is

selected with the MTRRs and the PCD and PWT bits in the page-table or page-directory entry for the page. Table

11-6 describes the mapping of MTRR memory types and page-level caching attributes to effective memory types,

when normal caching is in effect (the CD and NW flags in control register CR0 are clear). Combinations that appear

in gray are implementation-defined for the Pentium Pro and Pentium II processors. System designers are encour-

aged to avoid these implementation-defined combinations.

When normal caching is in effect, the effective memory type shown in Table 11-6 is determined using the following

rules:

1. If the PCD and PWT attributes for the page are both 0, then the effective memory type is identical to the

MTRR-defined memory type.

Table 11-6. Effective Page-Level Memory Type for Pentium Pro and Pentium II Processors

MTRR Memory Type

1

PCD Value

PWT Value

Effective Memory Type

UC

X

X

UC

WC

0

0

WC

0

1

WC

1

0

WC

1

1

UC

WT

0

X

WT

1

X

UC

WP

0

0

WP

0

1

WP

1

0

WC

1

1

UC

WB

0

0

WB

0

1

WT

1

X

UC

NOTE:

1. These effective memory types also apply to the Pentium 4, Intel Xeon, and Pentium III processors when the PAT bit is not used

(set to 0) in page-table and page-directory entries.