Vol. 3A 10-47

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

10.13.2 EOI

Message

Local APICs send 14-cycle EOI messages to the I/O APIC to indicate that a level triggered interrupt has been

accepted by the processor. This interrupt, in turn, is a result of software writing into the EOI register of the local

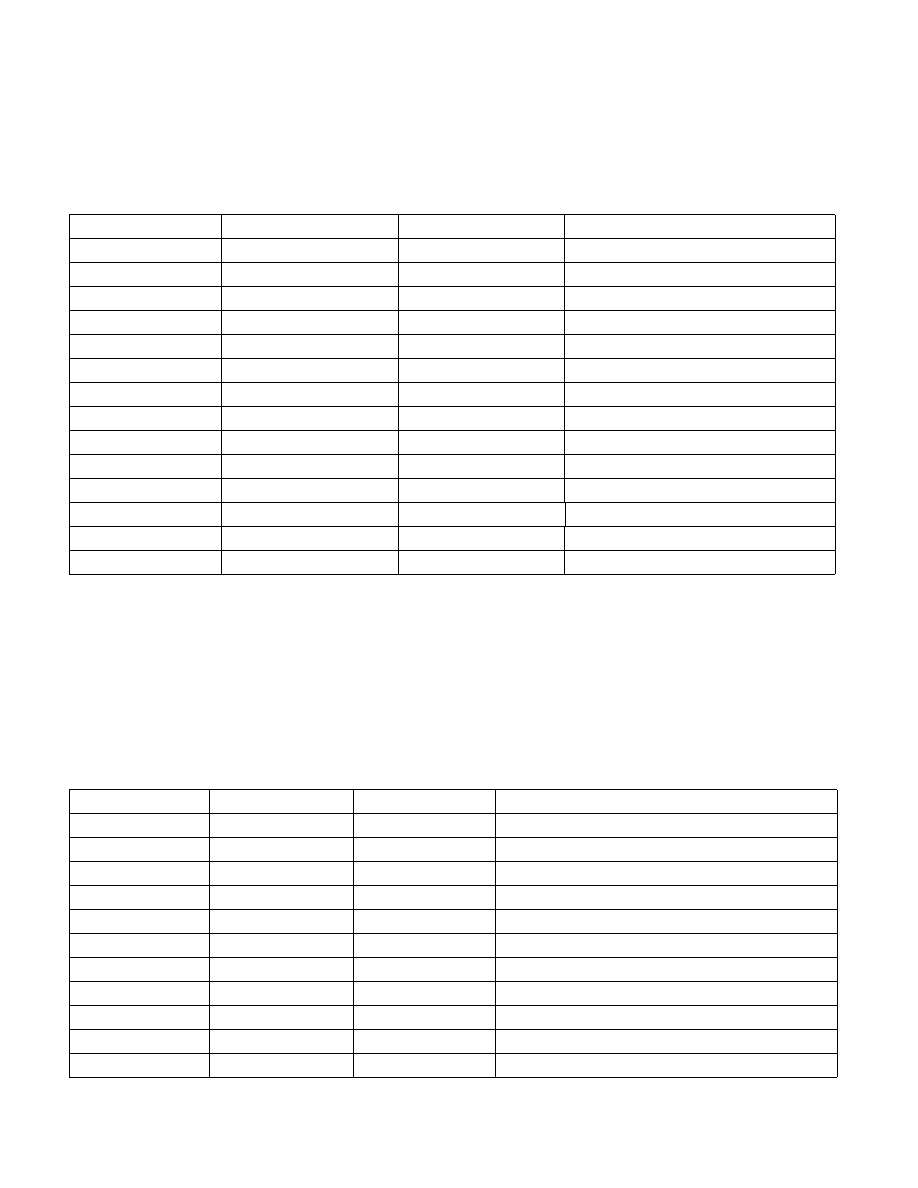

APIC. Table 10-1 shows the cycles in an EOI message.

The checksum is computed for cycles 6 through 9. It is a cumulative sum of the 2-bit (Bit1:Bit0) logical data values.

The carry out of all but the last addition is added to the sum. If any APIC computes a different checksum than the

one appearing on the bus in cycle 10, it signals an error, driving 11 on the APIC bus during cycle 12. In this case,

the APICs disregard the message. The sending APIC will receive an appropriate error indication (see Section

10.5.3, “Error Handling”) and resend the message. The status cycles are defined in Table 10-4.

10.13.2.1 Short Message

Short messages (21-cycles) are used for sending fixed, NMI, SMI, INIT, start-up, ExtINT and lowest-priority-with-

focus interrupts. Table 10-2 shows the cycles in a short message.

Table 10-1. EOI Message (14 Cycles)

Cycle

Bit1

Bit0

1

1

1

11 = EOI

2

ArbID3

0

Arbitration ID bits 3 through 0

3

ArbID2

0

4

ArbID1

0

5

ArbID0

0

6

V7

V6

Interrupt vector V7 - V0

7

V5

V4

8

V3

V2

9

V1

V0

10

C

C

Checksum for cycles 6 - 9

11

0

0

12

A

A

Status Cycle 0

13

A1

A1

Status Cycle 1

14

0

0

Idle

Table 10-2. Short Message (21 Cycles)

Cycle

Bit1

Bit0

1

0

1

0 1 = normal

2

ArbID3

0

Arbitration ID bits 3 through 0

3

ArbID2

0

4

ArbID1

0

5

ArbID0

0

6

DM

M2

DM = Destination Mode

7

M1

M0

M2-M0 = Delivery mode

8

L

TM

L = Level, TM = Trigger Mode

9

V7

V6

V7-V0 = Interrupt Vector

10

V5

V4

11

V3

V2