Vol. 3A 10-19

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

The ICR consists of the following fields.

Vector

The vector number of the interrupt being sent.

Delivery Mode

Specifies the type of IPI to be sent. This field is also know as the IPI message type field.

000 (Fixed)

Delivers the interrupt specified in the vector field to the target processor or

processors.

001 (Lowest Priority)

Same as fixed mode, except that the interrupt is delivered to the proces-

sor executing at the lowest priority among the set of processors specified

in the destination field. The ability for a processor to send a lowest priority

IPI is model specific and should be avoided by BIOS and operating system

software.

010 (SMI)

Delivers an SMI interrupt to the target processor or processors. The vector

field must be programmed to 00H for future compatibility.

011 (Reserved)

100 (NMI)

Delivers an NMI interrupt to the target processor or processors. The vector

information is ignored.

101 (INIT)

Delivers an INIT request to the target processor or processors, which

causes them to perform an INIT. As a result of this IPI message, all the tar-

get processors perform an INIT. The vector field must be programmed to

00H for future compatibility.

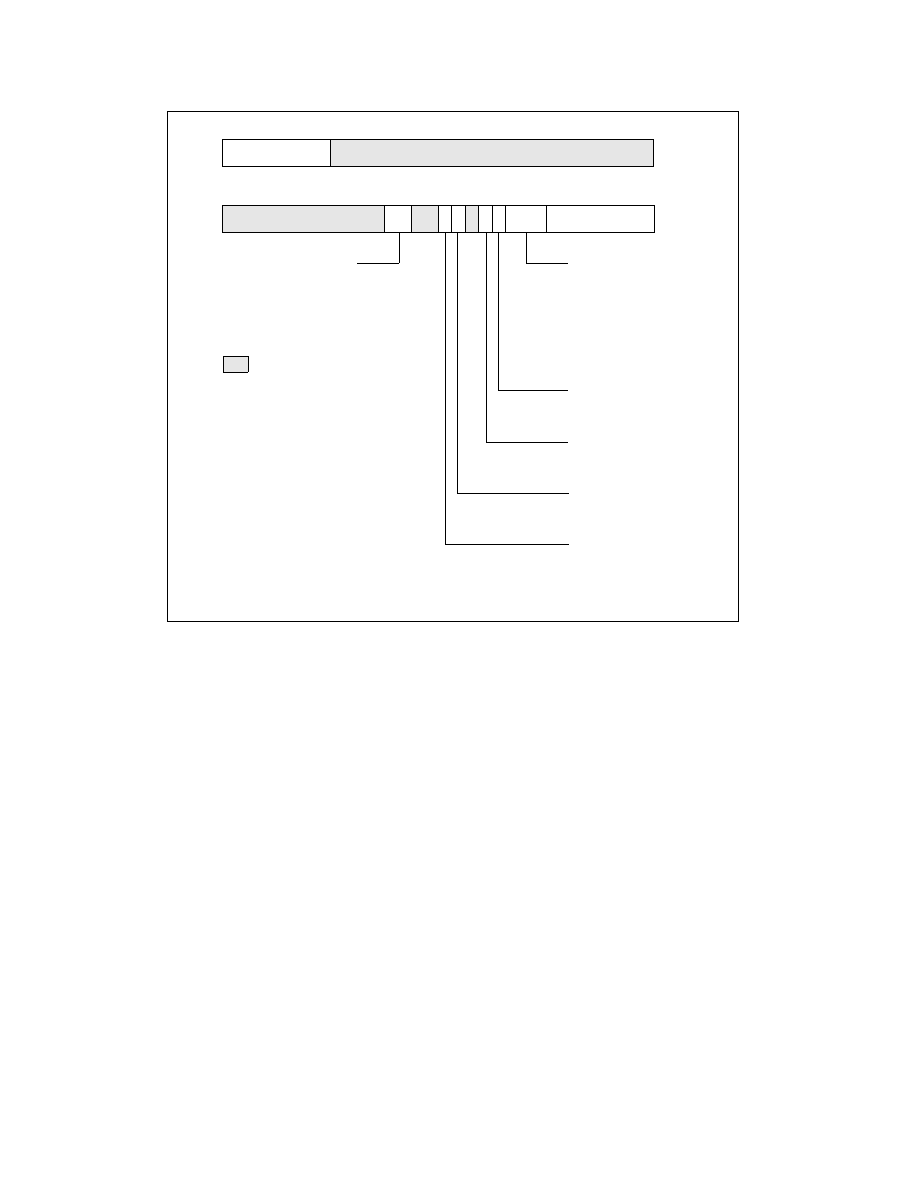

Figure 10-12. Interrupt Command Register (ICR)

31

0

Reserved

7

Vector

Destination Shorthand

8

10

Delivery Mode

000: Fixed

001: Lowest Priority

1

00: No Shorthand

01: Self

11

12

13

14

15

16

17

18

19

10: All Including Self

11: All Excluding Self

010: SMI

011: Reserved

100: NMI

101: INIT

110: Start Up

111: Reserved

Destination Mode

0: Physical

1: Logical

Delivery Status

0: Idle

1: Send Pending

Level

0 = De-assert

1 = Assert

Trigger Mode

0: Edge

1: Level

63

32

Reserved

Destination Field

56

Address: FEE0 0300H (0 - 31)

Value after Reset: 0H

Reserved

20

55

FEE0 0310H (32 - 63)

NOTE:

1. The ability of a processor to send Lowest Priority IPI is model specific.