10-36 Vol. 3A

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

f.

111B (ExtINT) — Deliver the signal to the INTR signal of all agents in the destination field (as an interrupt

that originated from an 8259A compatible interrupt controller). The vector is supplied by the INTA cycle

issued by the activation of the ExtINT. ExtINT is an edge triggered interrupt.

3. Level — Edge triggered interrupt messages are always interpreted as assert messages. For edge triggered

interrupts this field is not used. For level triggered interrupts, this bit reflects the state of the interrupt input.

4. Trigger Mode — This field indicates the signal type that will trigger a message.

a. 0 — Indicates edge sensitive.

b. 1 — Indicates level sensitive.

10.12 EXTENDED

XAPIC

(X2APIC)

The x2APIC architecture extends the xAPIC architecture (described in Section 9.4) in a backward compatible

manner and provides forward extendability for future Intel platform innovations. Specifically, the x2APIC architec-

ture does the following:

•

Retains all key elements of compatibility to the xAPIC architecture:

— delivery modes,

— interrupt and processor priorities,

— interrupt sources,

— interrupt destination types;

•

Provides extensions to scale processor addressability for both the logical and physical destination modes;

•

Adds new features to enhance performance of interrupt delivery;

•

Reduces complexity of logical destination mode interrupt delivery on link based platform architectures.

•

Uses MSR programming interface to access APIC registers in x2APIC mode instead of memory-mapped

interfaces. Memory-mapped interface is supported when operating in xAPIC mode.

10.12.1 Detecting and Enabling x2APIC Mode

Processor support for x2APIC mode can be detected by executing CPUID with EAX=1 and then checking ECX, bit 21

ECX. If CPUID.(EAX=1):ECX.21 is set , the processor supports the x2APIC capability and can be placed into the

x2APIC mode.

System software can place the local APIC in the x2APIC mode by setting the x2APIC mode enable bit (bit 10) in the

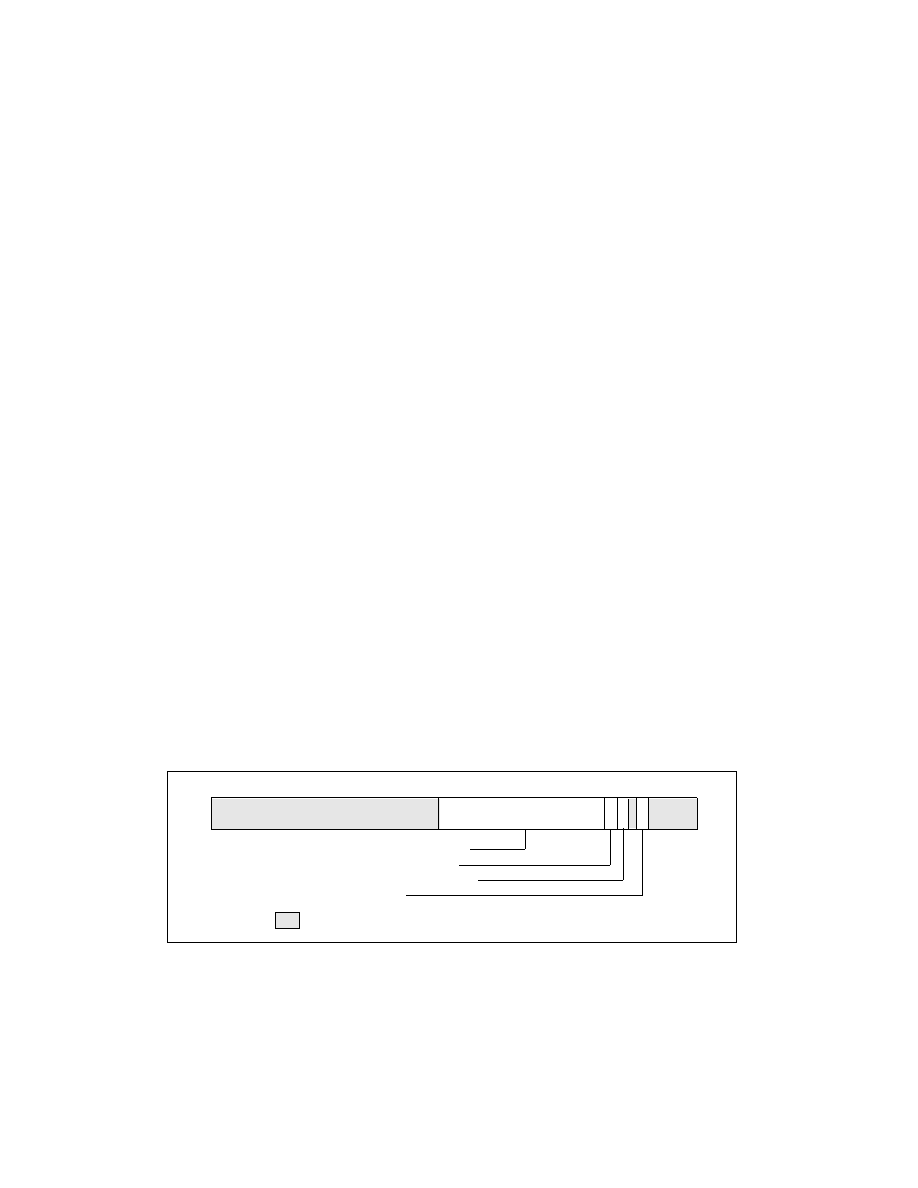

IA32_APIC_BASE MSR at MSR address 01BH. The layout for the IA32_APIC_BASE MSR is shown in Figure 10-26.

Table 10-5, “x2APIC operating mode configurations” describe the possible combinations of the enable bit (EN - bit

11) and the extended mode bit (EXTD - bit 10) in the IA32_APIC_BASE MSR.

Figure 10-26. IA32_APIC_BASE MSR Supporting x2APIC

BSP—Processor is BSP

EN—xAPIC global enable/disable

APIC Base—Base physical address

63

0

7

10

11

8

9

12

Reserved

36 35

APIC Base

Reserved

EXTD—Enable x2APIC mode