Vol. 3A 10-9

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

10.4.5

Relocating the Local APIC Registers

The Pentium 4, Intel Xeon, and P6 family processors permit the starting address of the APIC registers to be relo-

cated from FEE00000H to another physical address by modifying the value in the 24-bit base address field of the

IA32_APIC_BASE MSR. This extension of the APIC architecture is provided to help resolve conflicts with memory

maps of existing systems and to allow individual processors in an MP system to map their APIC registers to

different locations in physical memory.

10.4.6

Local APIC ID

At power up, system hardware assigns a unique APIC ID to each local APIC on the system bus (for Pentium 4 and

Intel Xeon processors) or on the APIC bus (for P6 family and Pentium processors). The hardware assigned APIC ID

is based on system topology and includes encoding for socket position and cluster information (see Figure 8-2).

In MP systems, the local APIC ID is also used as a processor ID by the BIOS and the operating system. Some

processors permit software to modify the APIC ID. However, the ability of software to modify the APIC ID is

processor model specific. Because of this, operating system software should avoid writing to the local APIC ID

register. The value returned by bits 31-24 of the EBX register (when the CPUID instruction is executed with a

source operand value of 1 in the EAX register) is always the Initial APIC ID (determined by the platform initializa-

tion). This is true even if software has changed the value in the Local APIC ID register.

The processor receives the hardware assigned APIC ID (or Initial APIC ID) by sampling pins A11# and A12# and

pins BR0# through BR3# (for the Pentium 4, Intel Xeon, and P6 family processors) and pins BE0# through BE3#

(for the Pentium processor). The APIC ID latched from these pins is stored in the APIC ID field of the local APIC ID

register (see Figure 10-6), and is used as the Initial APIC ID for the processor.

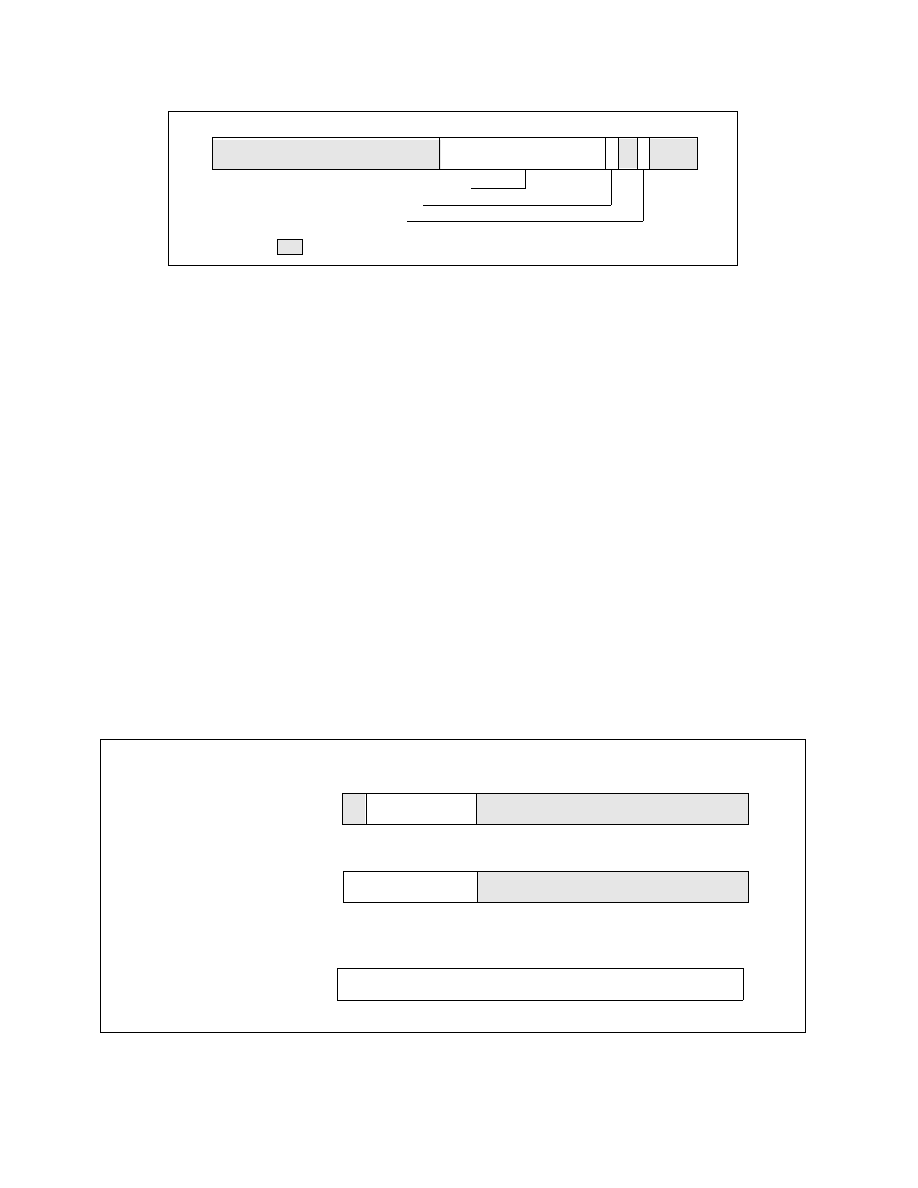

Figure 10-5. IA32_APIC_BASE MSR (APIC_BASE_MSR in P6 Family)

Figure 10-6. Local APIC ID Register

BSP—Processor is BSP

APIC global enable/disable

APIC Base—Base physical address

63

0

7

10

11

8

9

12

Reserved

MAXPHYADDR

APIC Base

Reserved

31

27

24

0

Reserved

APIC ID

Address: 0FEE0 0020H

Value after reset: 0000 0000H

P6 family and Pentium processors

Pentium 4 processors, Xeon processors, and later processors

31

24

0

Reserved

APIC ID

MSR Address: 802H

31

0

x2APIC ID

x2APIC Mode

xAPIC Mode