Vol. 3A 8-53

MULTIPLE-PROCESSOR MANAGEMENT

•

Boot IPI (BIPI)—Initiates the arbitration mechanism that selects a BSP from the group of processors on the

system bus and designates the remainder of the processors as APs. Each processor on the system bus

broadcasts a BIPI to all the processors following a power-up or RESET.

•

Final Boot IPI (FIPI)—Initiates the BIOS initialization procedure for the BSP. This IPI is broadcast to all the

processors on the system bus, but only the BSP responds to it. The BSP responds by beginning execution of the

BIOS initialization code at the reset vector.

•

Startup IPI (SIPI)—Initiates the initialization procedure for an AP. The SIPI message contains a vector to the AP

initialization code in the BIOS.

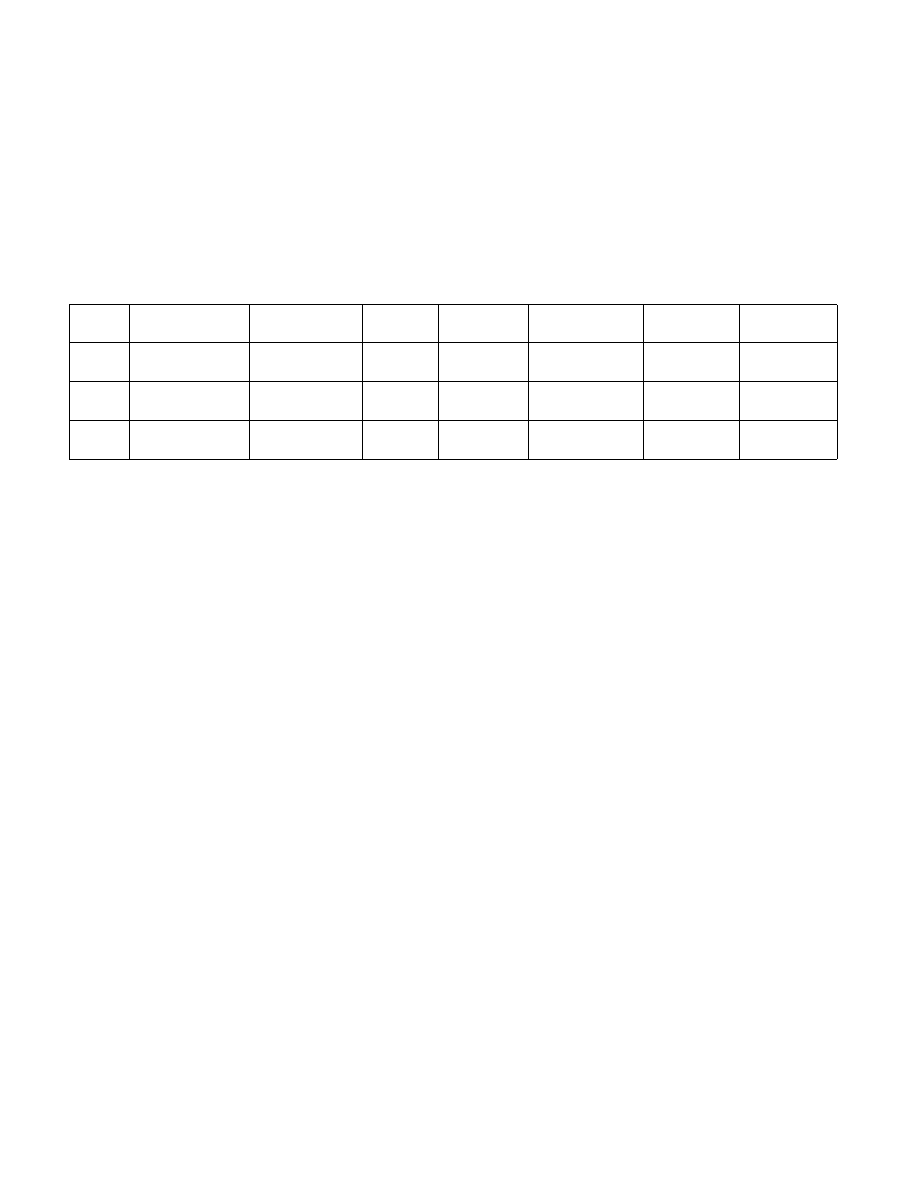

Table 8-5 describes the various fields of the boot phase IPIs.

For BIPI messages, the lower 4 bits of the vector field contain the APIC ID of the processor issuing the message and

the upper 4 bits contain the “generation ID” of the message. All P6 family processor will have a generation ID of

4H. BIPIs will therefore use vector values ranging from 40H to 4EH (4FH can not be used because FH is not a valid

APIC ID).

8.11.2

MP Initialization Protocol Algorithm

Following a power-up or RESET of a system, the P6 family processors in the system execute the MP initialization

protocol algorithm to initialize each of the processors on the system bus. In the course of executing this algorithm,

the following boot-up and initialization operations are carried out:

1. Each processor on the system bus is assigned a unique APIC ID, based on system topology (see Section 8.4.5,

“Identifying Logical Processors in an MP System”). This ID is written into the local APIC ID register for each

processor.

2. Each processor executes its internal BIST simultaneously with the other processors on the system bus. Upon

completion of the BIST (at T0), each processor broadcasts a BIPI to “all including self” (see Figure 8-1).

3. APIC arbitration hardware causes all the APICs to respond to the BIPIs one at a time (at T1, T2, T3, and T4).

4. When the first BIPI is received (at time T1), each APIC compares the four least significant bits of the BIPI’s

vector field with its APIC ID. If the vector and APIC ID match, the processor selects itself as the BSP by setting

the BSP flag in its IA32_APIC_BASE MSR. If the vector and APIC ID do not match, the processor selects itself

as an AP by entering the “wait for SIPI” state. (Note that in Figure 8-1, the BIPI from processor 1 is the first

BIPI to be handled, so processor 1 becomes the BSP.)

5. The newly established BSP broadcasts an FIPI message to “all including self.” The FIPI is guaranteed to be

handled only after the completion of the BIPIs that were issued by the non-BSP processors.

Table 8-5. Boot Phase IPI Message Format

Type

Destination

Field

Destination

Shorthand

Trigger

Mode

Level

Destination

Mode

Delivery

Mode

Vector

(Hex)

BIPI

Not used

All including self

Edge

Deassert

Don’t Care

Fixed

(000)

40 to 4E*

FIPI

Not used

All including self

Edge

Deassert

Don’t Care

Fixed

(000)

10

SIPI

Used

All excluding self

Edge

Assert

Physical

StartUp

(110)

00 to FF

NOTE:

* For all P6 family processors.