Vol. 3A 8-27

MULTIPLE-PROCESSOR MANAGEMENT

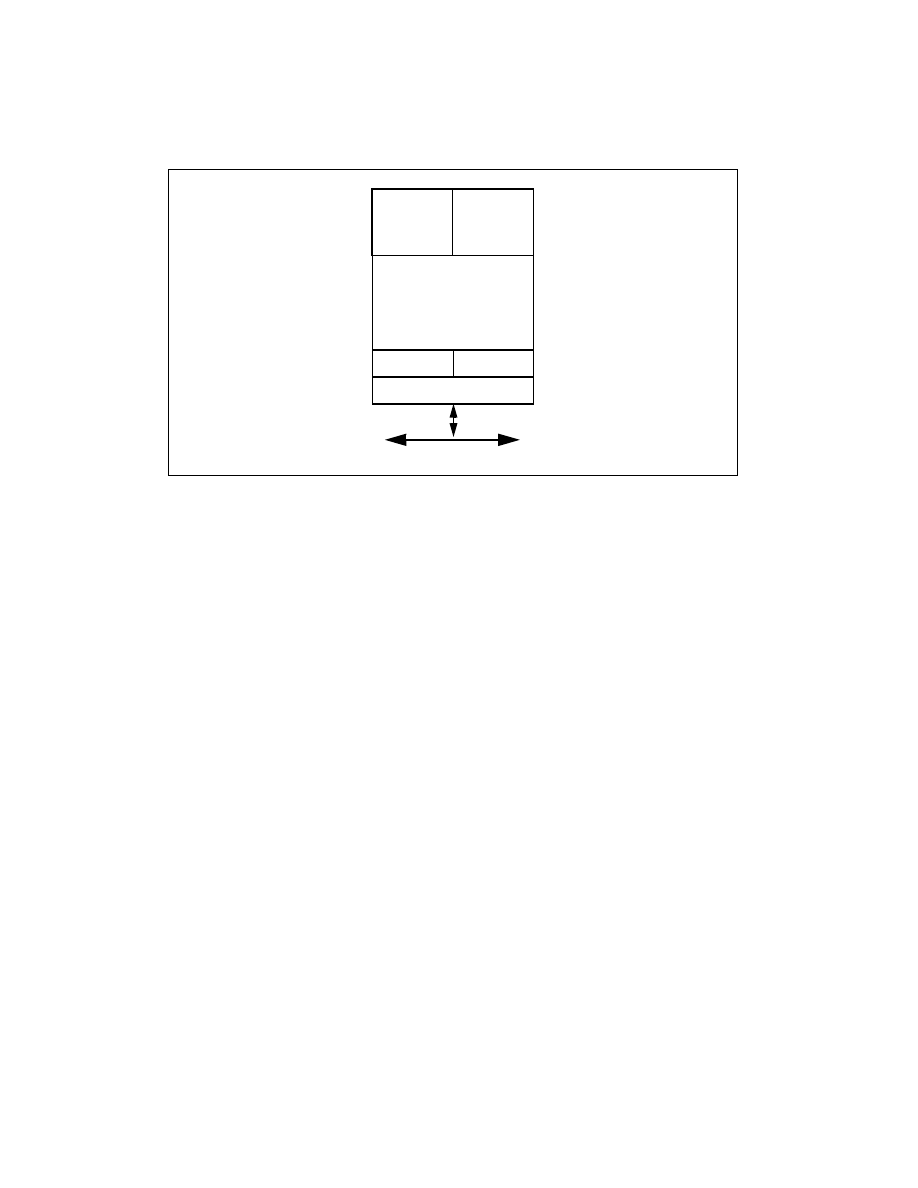

consists of two logical processors (each represented by a separate architectural state) which share the processor’s

execution engine and the bus interface. Each logical processor also has its own advanced programmable interrupt

controller (APIC).

8.7.1

State of the Logical Processors

The following features are part of the architectural state of logical processors within Intel 64 or IA-32 processors

supporting Intel Hyper-Threading Technology. The features can be subdivided into three groups:

•

Duplicated for each logical processor

•

Shared by logical processors in a physical processor

•

Shared or duplicated, depending on the implementation

The following features are duplicated for each logical processor:

•

General purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, ESP, and EBP)

•

Segment registers (CS, DS, SS, ES, FS, and GS)

•

EFLAGS and EIP registers. Note that the CS and EIP/RIP registers for each logical processor point to the

instruction stream for the thread being executed by the logical processor.

•

x87 FPU registers (ST0 through ST7, status word, control word, tag word, data operand pointer, and instruction

pointer)

•

MMX registers (MM0 through MM7)

•

XMM registers (XMM0 through XMM7) and the MXCSR register

•

Control registers and system table pointer registers (GDTR, LDTR, IDTR, task register)

•

Debug registers (DR0, DR1, DR2, DR3, DR6, DR7) and the debug control MSRs

•

Machine check global status (IA32_MCG_STATUS) and machine check capability (IA32_MCG_CAP) MSRs

•

Thermal clock modulation and ACPI Power management control MSRs

•

Time stamp counter MSRs

•

Most of the other MSR registers, including the page attribute table (PAT). See the exceptions below.

•

Local APIC registers.

•

Additional general purpose registers (R8-R15), XMM registers (XMM8-XMM15), control register, IA32_EFER on

Intel 64 processors.

The following features are shared by logical processors:

Figure 8-4. IA-32 Processor with Two Logical Processors Supporting Intel HT Technology

Logical

Processor 0

Architectural

State

Bus Interface

Local APIC

Local APIC

Logical

Processor 1

Architectural

State

Execution Engine

System Bus