38-6 Vol. 3D

ENCLAVE ACCESS CONTROL AND DATA STRUCTURES

38.8

THREAD CONTROL STRUCTURE (TCS)

Each executing thread in the enclave is associated with a Thread Control Structure. It requires 4K-Bytes alignment.

38.8.1 TCS.FLAGS

38.8.2

State Save Area Offset (OSSA)

The OSSA points to a stack of State Save Area (SSA) frames (see Section 38.9) used to save the processor state

when an interrupt or exception occurs while executing in the enclave.

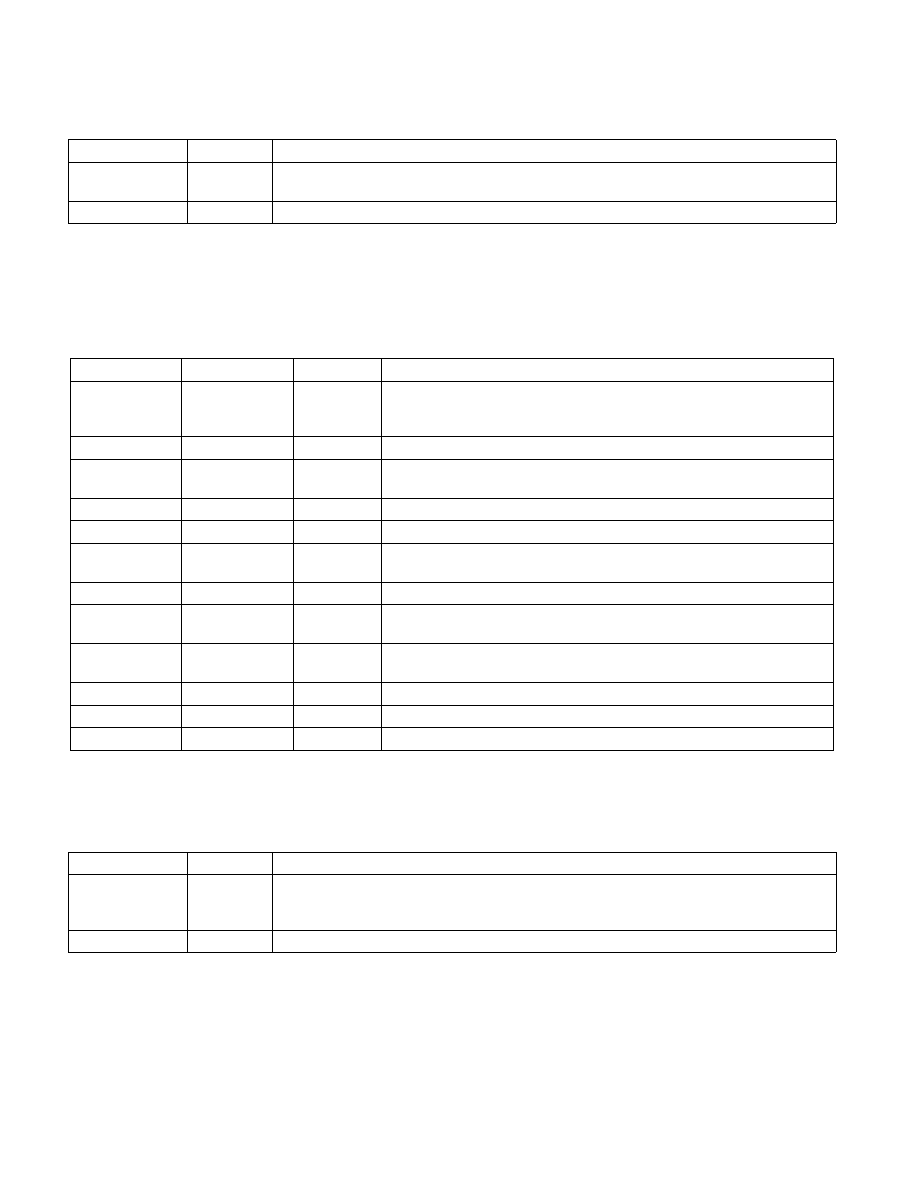

Table 38-4. Bit Vector Layout of MISCSELECT Field of Extended Information

Field

Bit Position

Description

EXINFO

0

Report information about page fault and general protection exception that occurred inside an

enclave.

Reserved

31:1

Reserved (0).

Table 38-5. Layout of Thread Control Structure (TCS)

Field

OFFSET (Bytes) Size (Bytes)

Description

STAGE

0

8

Enclave execution state of the thread controlled by this TCS. A value of 0 indi-

cates that this TCS is available for enclave entry. A value of 1 indicates that a

processer is currently executing an enclave in the context of this TCS.

FLAGS

8

8

The thread’s execution flags (see Section 38.8.1).

OSSA

16

8

Offset of the base of the State Save Area stack, relative to the enclave base.

Must be page aligned.

CSSA

24

4

Current slot index of an SSA frame, cleared by EADD and EACCEPT.

NSSA

28

4

Number of available slots for SSA frames.

OENTRY

32

8

Offset in enclave to which control is transferred on EENTER relative to the

base of the enclave.

AEP

40

8

The value of the Asynchronous Exit Pointer that was saved at EENTER time.

OFSBASGX

48

8

Offset to add to the base address of the enclave for producing the base

address of FS segment inside the enclave. Must be page aligned.

OGSBASGX

56

8

Offset to add to the base address of the enclave for producing the base

address of GS segment inside the enclave. Must be page aligned.

FSLIMIT

64

4

Size to become the new FS limit in 32-bit mode.

GSLIMIT

68

4

Size to become the new GS limit in 32-bit mode.

RESERVED

72

4024

Must be zero.

Table 38-6. Layout of TCS.FLAGS Field

Field

Bit Position

Description

DBGOPTIN

0

If set, allows debugging features (single-stepping, breakpoints, etc.) to be enabled and active while

executing in the enclave on this TCS. Hardware clears this bit on EADD. A debugger may later mod-

ify it if the enclave’s ATTRIBUTES.DEBUG is set.

RESERVED

63:1