Vol. 3D 38-7

ENCLAVE ACCESS CONTROL AND DATA STRUCTURES

38.8.3

Current State Save Area Frame (CSSA)

CSSA is the index of the current SSA frame that will be used by the processor to determine where to save the

processor state on an interrupt or exception that occurs while executing in the enclave. It is an index into the array

of frames addressed by OSSA. CSSA is incremented on an AEX and decremented on an ERESUME.

38.8.4

Number of State Save Area Frames (NSSA)

NSSA specifies the number of SSA frames available for this TCS. There must be at least one available SSA frame

when EENTER-ing the enclave or the EENTER will fail.

38.9

STATE SAVE AREA (SSA) FRAME

When an AEX occurs while running in an enclave, the architectural state is saved in the thread’s current SSA frame,

which is pointed to by TCS.CSSA. An SSA frame must be page aligned, and contains the following regions:

•

The XSAVE region starts at the base of the SSA frame, this region contains extended feature register state in

an XSAVE/FXSAVE-compatible non-compacted format.

•

A Pad region: software may choose to maintain a pad region separating the XSAVE region and the MISC region.

Software choose the size of the pad region according to the sizes of the MISC and GPRSGX regions.

•

The GPRSGX region. The GPRSGX region is the last region of an SSA frame (see Table 38-7). This is used to

hold the processor general purpose registers (RAX … R15), the RIP, the outside RSP and RBP, RFLAGS and the

AEX information.

•

The MISC region (If CPUIDEAX=12H, ECX=0):EBX[31:0] != 0). The MISC region is adjacent to the GRPSGX

region, and may contain zero or more components of extended information that would be saved when an AEX

occurs. If the MISC region is absent, the region between the GPRSGX and XSAVE regions is the pad region that

software can use. If the MISC region is present, the region between the MISC and XSAVE regions is the pad

region that software can use. See additional details in Section 38.9.2.

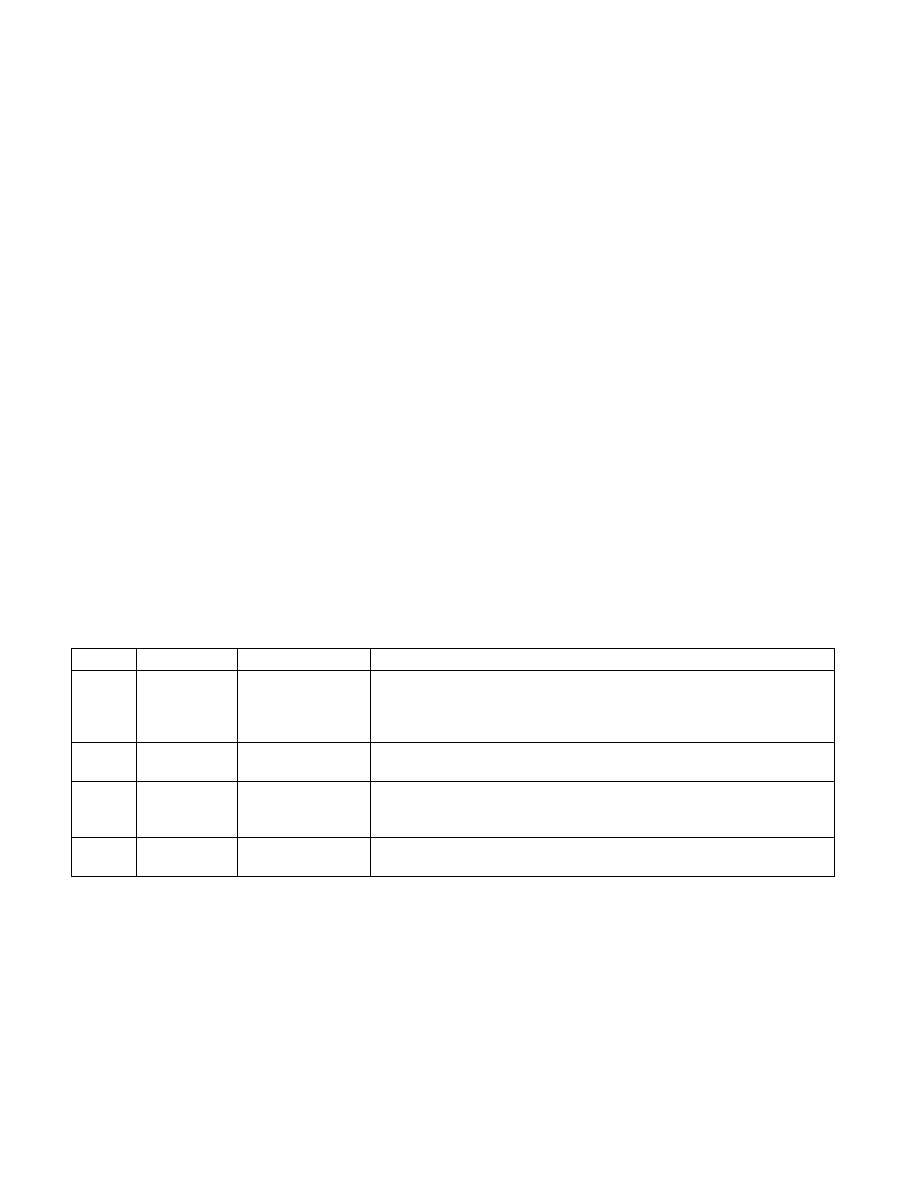

Table 38-7. Top-to-Bottom Layout of an SSA Frame

Region

Offset (Byte)

Size (Bytes)

Description

XSAVE

0

Calculate using CPUID

leaf 0DH information

The size of XSAVE region in SSA is derived from the enclave’s support of the col-

lection of processor extended states that would be managed by XSAVE. The

enablement of those processor extended state components in conjunction with

CPUID leaf 0DH information determines the XSAVE region size in SSA.

Pad

End of XSAVE

region

Chosen by enclave

writer

Ensure the end of GPRSGX region is aligned to the end of a 4KB page.

MISC

base of GPRSGX

– sizeof(MISC)

Calculate from high-

est set bit of

SECS.MISCSELECT

See Section 38.9.2.

GPRSGX

SSAFRAMESIZE

– 176

176

See Table 38-8 for layout of the GPRSGX region.