38-4 Vol. 3D

ENCLAVE ACCESS CONTROL AND DATA STRUCTURES

38.6

INTEL® SGX DATA STRUCTURES OVERVIEW

Enclave operation is managed via a collection of data structures. Many of the top-level data structures contain sub-

structures. The top-level data structures relate to parameters that may be used in enclave setup/maintenance, by

Intel SGX instructions, or AEX event. The top-level data structures are:

•

SGX Enclave Control Structure (SECS)

•

Thread Control Structure (TCS)

•

State Save Area (SSA)

•

Page Information (PAGEINFO)

•

Security Information (SECINFO)

•

Paging Crypto MetaData (PCMD)

•

Enclave Signature Structure (SIGSTRUCT)

•

EINIT Token Structure (EINITTOKEN)

•

Report Structure (REPORT)

•

Report Target Info (TARGETINFO)

•

Key Request (KEYREQUEST)

•

Version Array (VA)

•

Enclave Page Cache Map (EPCM)

Details of the top-level data structures and associated sub-structures are listed in Section 38.7 through Section

38.19.

38.7

SGX ENCLAVE CONTROL STRUCTURE (SECS)

The SECS data structure requires 4K-Bytes alignment.

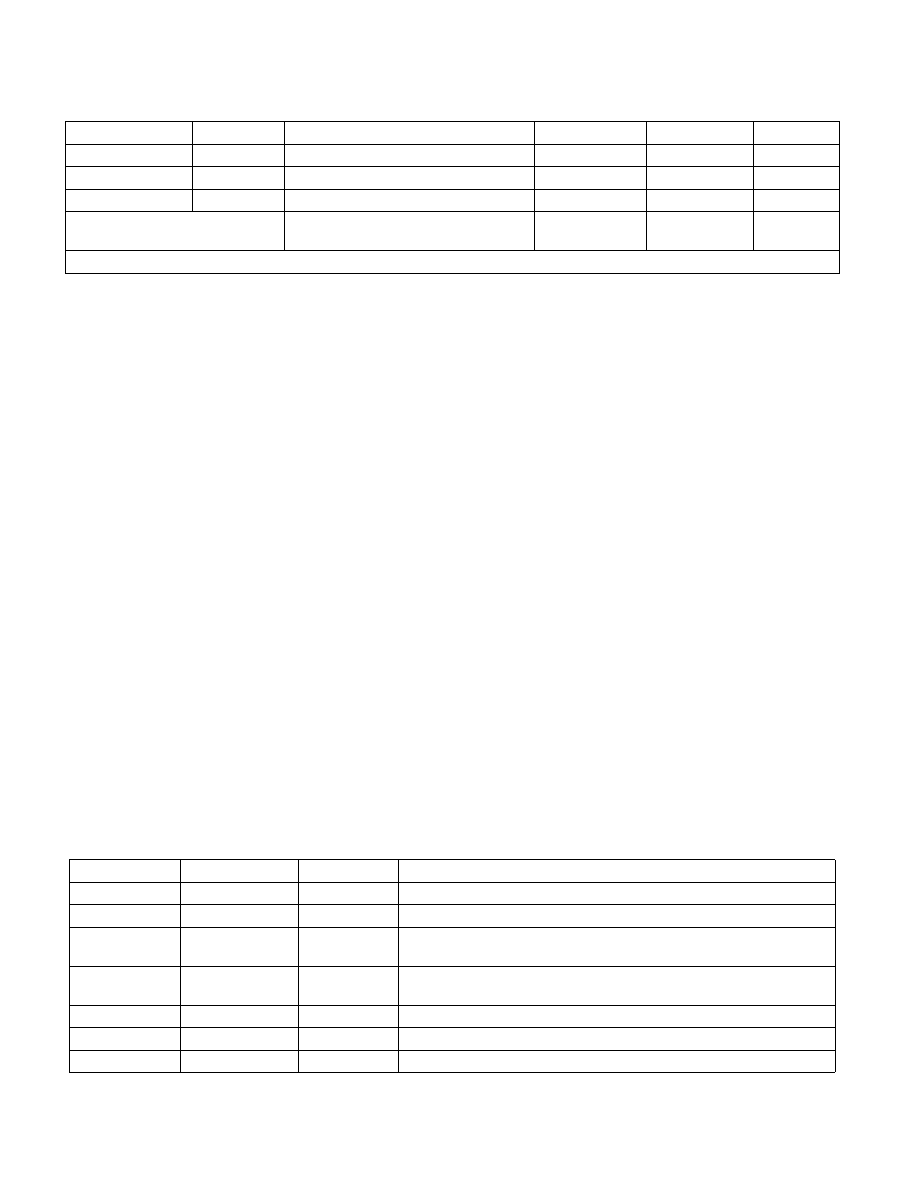

ERESUME

SGX1

TCS and linked SSA

SECS

ETRACK

SGX1

EPCPAGE

EWB

SGX1

PAGEINFO and linked structures, PCMD

EPCPAGE

VAPAGE

SECS

Asynchronous Enclave Exit*

SECS, TCS,

SSA

*Details of Asynchronous Enclave Exit (AEX) is described in Section 40.4

Table 38-2. Layout of SGX Enclave Control Structure (SECS)

Field

OFFSET (Bytes)

Size (Bytes)

Description

SIZE

0

8

Size of enclave in bytes; must be power of 2.

BASEADDR

8

8

Enclave Base Linear Address must be naturally aligned to size.

SSAFRAMESIZE

16

4

Size of one SSA frame in pages, including XSAVE, pad, GPR, and MISC (if

CPUID.(EAX=12H, ECX=0):.EBX != 0).

MISCSELECT

20

4

Bit vector specifying which extended features are saved to the MISC region

(see Section 38.7.2) of the SSA frame when an AEX occurs.

RESERVED

24

24

ATTRIBUTES

48

16

Attributes of the Enclave, see Table 38-3.

MRENCLAVE

64

32

Measurement Register of enclave build process. See SIGSTRUCT for format.

Table 38-1. List of Implicit and Explicit Memory Access by Intel® SGX Enclave Instructions (Contd.)

Instr. Leaf

Enum.

Explicit 1

Explicit 2

Explicit 3

Implicit