Vol. 3C 36-43

INTEL® PROCESSOR TRACE

36.4.2.6 Flow Update (FUP) Packet

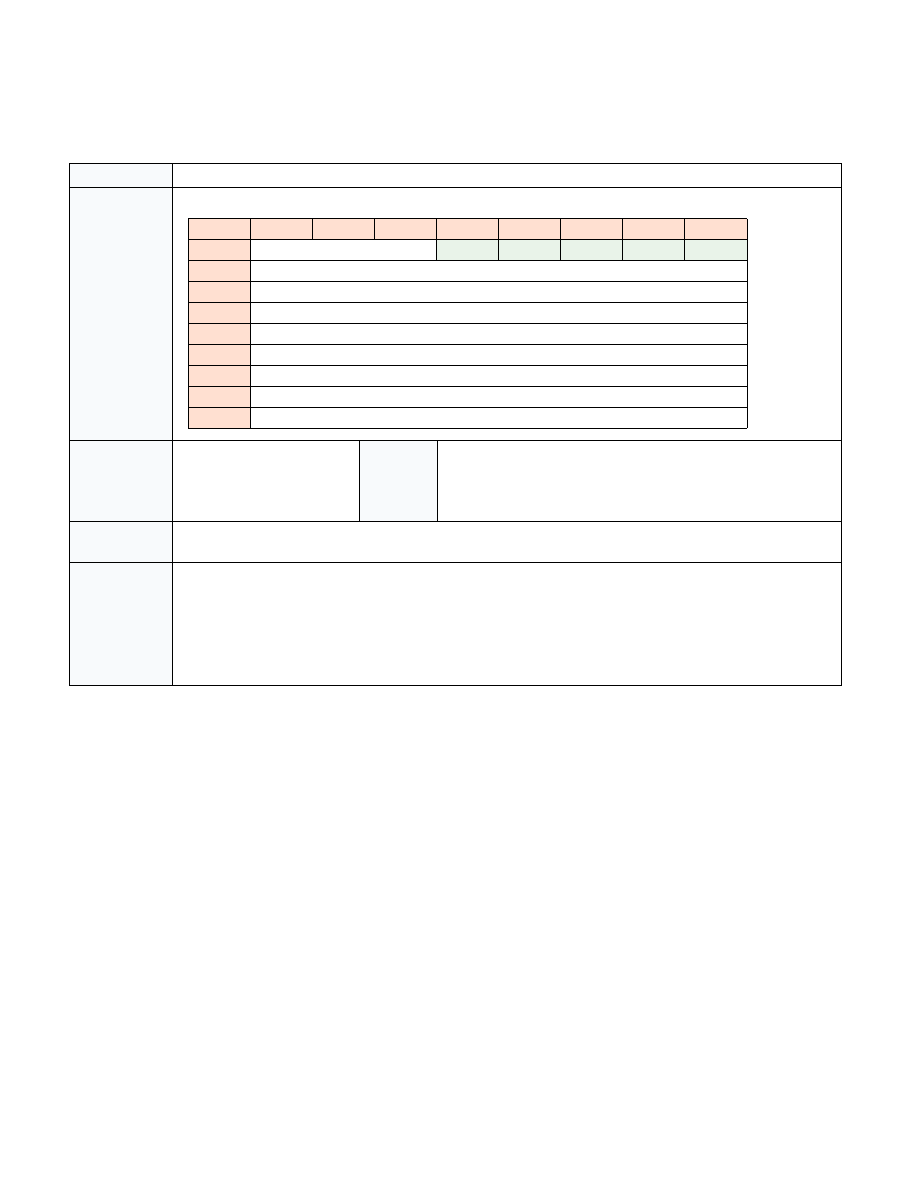

Table 36-22. FUP Packet Definition

Name

Flow Update (FUP) Packet

Packet Format

Dependencies

TriggerEn & ContextEn.

(Typically depends on

BranchEn and FilterEn as well,

see Section 36.2.4 for details.)

Generation

Scenario

Asynchronous Events (interrupts, exceptions, INIT, SIPI, SMI, VM

exit

1

, #MC), XBEGIN, XEND, XABORT, XACQUIRE, XRELEASE, (EEN-

TRY, EEXIT, ERESUME, EEE, AEX,)

2

, INT 0, INT 3, INT n, a WRMSR that

disables packet generation.

NOTES:

1. If IA32_VMX_MISC[bit 14] reports 1.

2. If Intel Software Guard Extensions is supported.

Description

Provides the source address for asynchronous events, and some other instructions. Is never sent alone, always sent

with an associated TIP or MODE packet, and potentially others.

Application

FUP packets provide the IP to which they bind. However, they are never standalone, but are coupled with other

packets.

In TSX cases, the FUP is immediately preceded by a MODE.TSX, which binds to the same IP. A TIP will follow only in

the case of TSX aborts, see Section 36.4.2.8 for details.

Otherwise, FUPs are part of compound packet events (see Section 36.4.1). In these compound cases, the FUP pro-

vides the source IP for an instruction or event, while a following TIP (or TIP.PGD) uop will provide any destination IP.

Other packets may be included in the compound event between the FUP and TIP.

7

6

5

4

3

2

1

0

0

IPBytes

1

1

1

0

1

1

IP[7:0]

2

IP[15:8]

3

IP[23:16]

4

IP[31:24]

5

IP[39:32]

6

IP[47:40]

7

IP[55:48]

8

IP[63:56]