36-46 Vol. 3C

INTEL® PROCESSOR TRACE

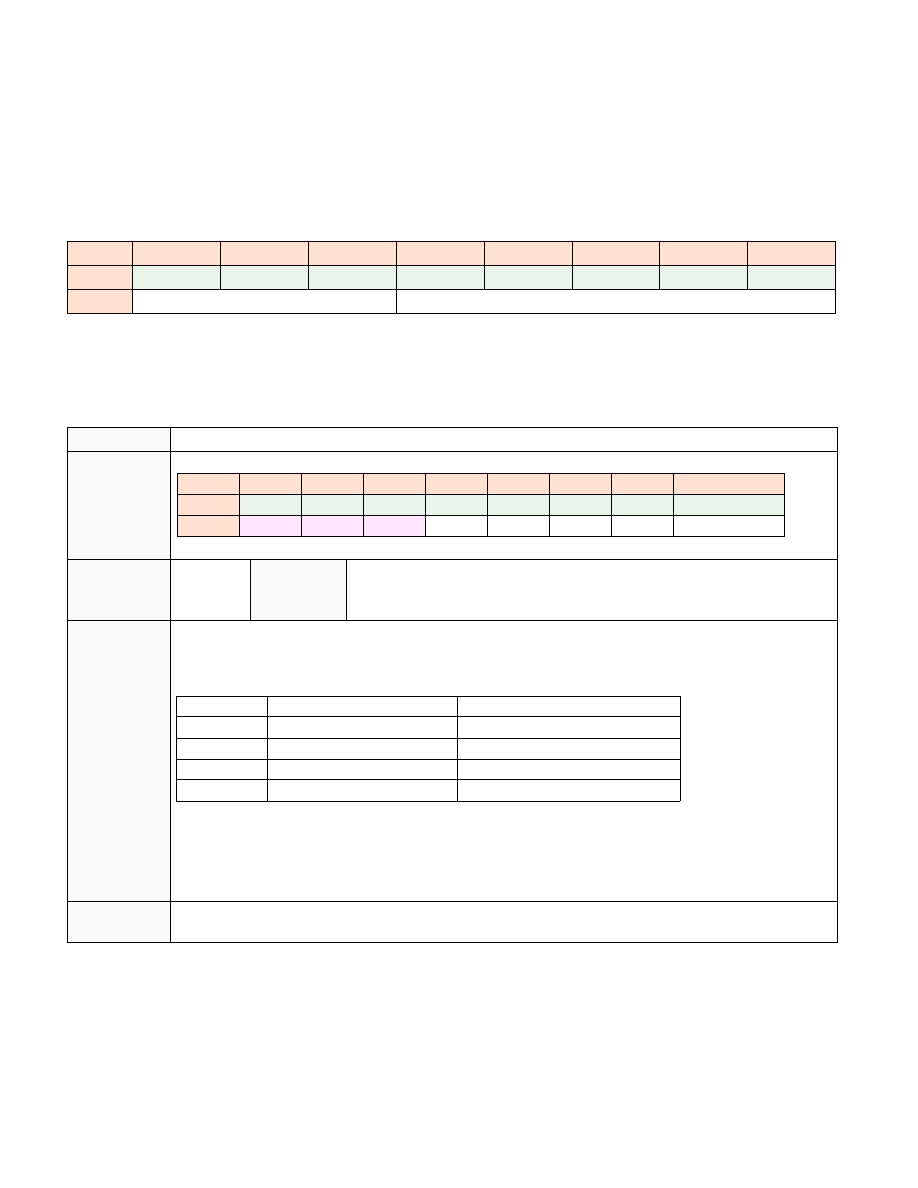

36.4.2.8 MODE Packets

MODE packets keep the decoder informed of various processor modes about which it needs to know in order to

properly manage the packet output, or to properly disassemble the associated binaries. MODE packets include a

header and a mode byte, as shown below.

The MODE Leaf ID indicates which set of mode bits are held in the lower bits.

MODE.Exec Packet

Table 36-25. General Form of MODE Packets

7

6

5

4

3

2

1

0

0

1

0

0

1

1

0

0

1

1

Leaf ID

Mode

Table 36-26. MODE.Exec Packet Definition

Name

MODE.Exec Packet

Packet Format

Dependencies

PacketEn

Generation

Scenario

Far branch, interrupt, exception, (VM exit, VM entry,)

1

if the mode changes.

PSB+, and any scenario that can generate a TIP.PGE, such that the mode may have

changed since the last MODE.Exec.

NOTES:

1. If IA32_VMX_MISC[bit 14] reports 1.

Description

Indicates whether software is in 16, 32, or 64-bit mode, by providing the CS.D and (CS.L & IA32_EFER.LMA) values.

Essential for the decoder to properly disassemble the associated binary.

MODE.Exec is sent at the time of a mode change, if PacketEn=1 at the time, or when tracing resumes, if necessary.

In the former case, the MODE.Exec packet is generated along with other packets that result from the far transfer

operation that changes the mode. In cases where the mode changes while PacketEn=0, the processor will send out

a MODE.Exec along with the TIP.PGE when tracing resumes. The processor may opt to suppress the MODE.Exec

when tracing resumes if the mode matches that from the last MODE.Exec packet, if there was no PSB in between.

Application

MODE.Exec always immediately precedes a TIP or TIP.PGE. The mode change applies to the IP address in the payload

of the next TIP or TIP.PGE.

7

6

5

4

3

2

1

0

0

1

0

0

1

1

0

0

1

1

0

0

0

0

0

0

CS.D

(CS.L & LMA)

CS.D

(CS.L & IA32_EFER.LMA)

Addressing Mode

1

1

N/A

0

1

64-bit mode

1

0

32-bit mode

0

0

16-bit mode