Vol. 3C 36-27

INTEL® PROCESSOR TRACE

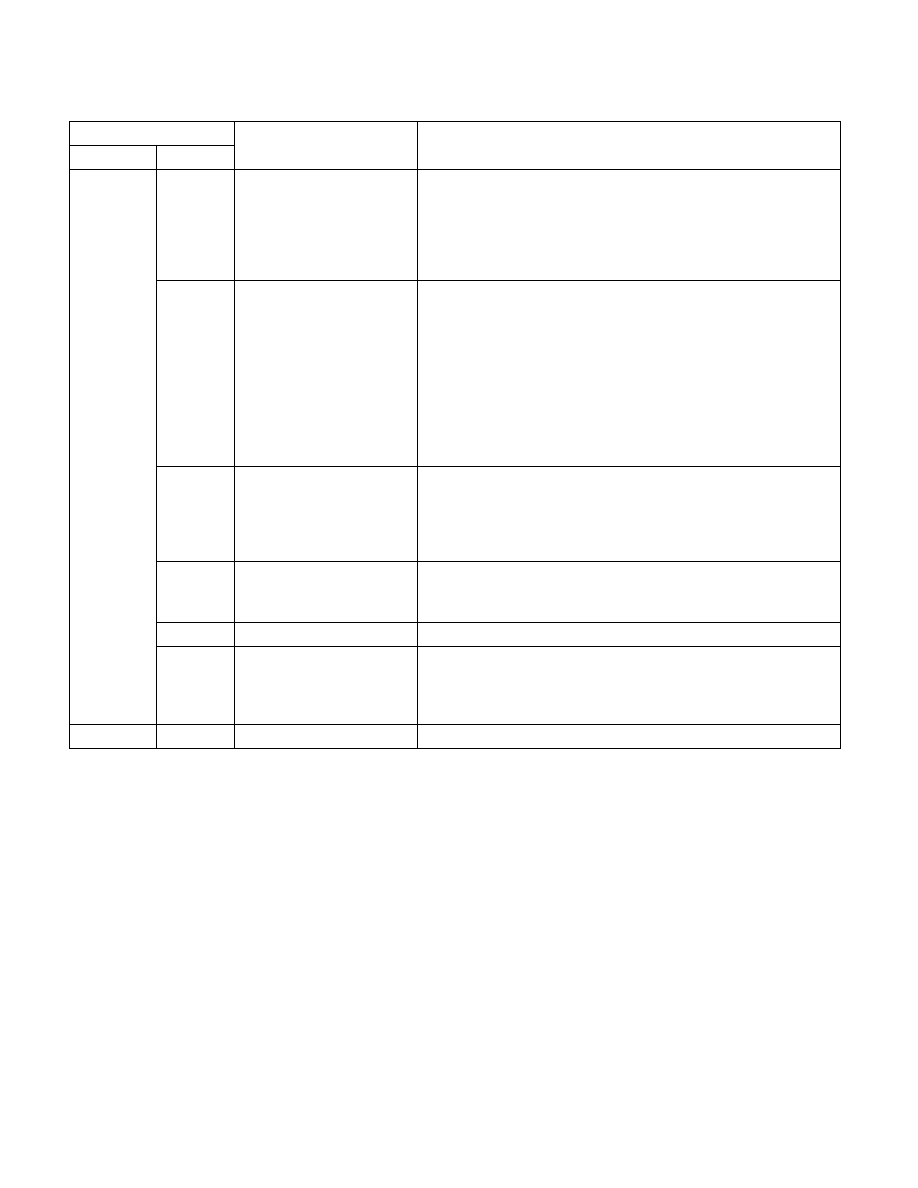

If CPUID.(EAX=14H, ECX=0):EAX reports a non-zero value, additional capabilities of Intel Processor Trace are

described in the sub-leaves of CPUID leaf 14H.

ECX

0

ToPA Output Supported

1: Tracing can be enabled with IA32_RTIT_CTL.ToPA = 1, hence utilizing

the ToPA output scheme (Section 36.2.6.2) IA32_RTIT_OUTPUT_BASE

and IA32_RTIT_OUTPUT_MASK_PTRS MSRs can be accessed.

0: Unless CPUID.(EAX=14H, ECX=0):ECX.SNGLRNGOUT[bit 2] = 1. writes

to IA32_RTIT_OUTPUT_BASE or IA32_RTIT_OUTPUT_MASK_PTRS.

MSRs will #GP fault.

1

ToPA Tables Allow Multiple

Output Entries

1: ToPA tables can hold any number of output entries, up to the

maximum allowed by the MaskOrTableOffset field of

IA32_RTIT_OUTPUT_MASK_PTRS.

0: ToPA tables can hold only one output entry, which must be followed

by an END=1 entry which points back to the base of the table.

Further, ToPA PMIs will be delivered before the region is filled. See ToPA

PMI in Section 36.2.6.2.

If there is more than one output entry before the END entry, or if the

END entry has the wrong base address, an operational error will be

signaled (see “ToPA Errors” in Section 36.2.6.2).

2

Single-Range Output

Supported

1: Enabling tracing (TraceEn=1) with IA32_RTIT_CTL.ToPA=0 is

supported.

0: Unless CPUID.(EAX=14H, ECX=0):ECX.TOPAOUT[bit 0] = 1. writes to

IA32_RTIT_OUTPUT_BASE or IA32_RTIT_OUTPUT_MASK_PTRS. MSRs

will #GP fault.

3

Output to Trace Transport

Subsystem Supported

1: Setting IA32_RTIT_CTL.FabricEn to 1 is supported.

0: IA32_RTIT_CTL.FabricEn is reserved. Write 1 to

IA32_RTIT_CTL.FabricEn will #GP fault.

30:4

Reserved

31

IP Payloads are LIP

1: Generated packets which contain IP payloads have LIP values, which

include the CS base component.

0: Generated packets which contain IP payloads have RIP values, which

are the offset from CS base.

EDX

31:0

Reserved

Table 36-11. CPUID Leaf 14H Enumeration of Intel Processor Trace Capabilities (Contd.)

CPUID.(EAX=14H,ECX=0)

Name

Description Behavior

Register

Bits