36-14 Vol. 3C

INTEL® PROCESSOR TRACE

ToPA Errors

When a malformed ToPA entry is found, an operation error results (see Section 36.3.9). A malformed entry can

be any of the following:

1. ToPA entry reserved bit violation.

This describes cases where a bit marked as reserved in Section 36.2.6.2 above is set to 1.

2. ToPA alignment violation.

This includes cases where illegal ToPA entry base address bits are set to 1:

a. ToPA table base address is not 4KB-aligned. The table base can be from a WRMSR to

IA32_RTIT_OUTPUT_BASE, or from a ToPA entry with END=1.

b. ToPA entry base address is not aligned to the ToPA entry size (e.g., a 2MB region with base address[20:12]

not equal to 0).

c. ToPA entry base address sets upper physical address bits not supported by the processor.

3. Illegal ToPA Output Offset (if IA32_RTIT_STATUS.Stopped=0).

IA32_RTIT_OUTPUT_MASK_PTRS.OutputOffset is greater than or equal to the size of the current ToPA output

region size.

4. ToPA rules violations.

These are similar to ToPA entry reserved bit violations; they are cases when a ToPA entry is encountered with

illegal field combinations. They include the following:

a. Setting the STOP or INT bit on an entry with END=1.

b. Setting the END bit in entry 0 of a ToPA table.

c. On processors that support only a single ToPA entry (see above), two additional illegal settings apply:

i) ToPA table entry 1 with END=0.

ii) ToPA table entry 1 with base address not matching the table base.

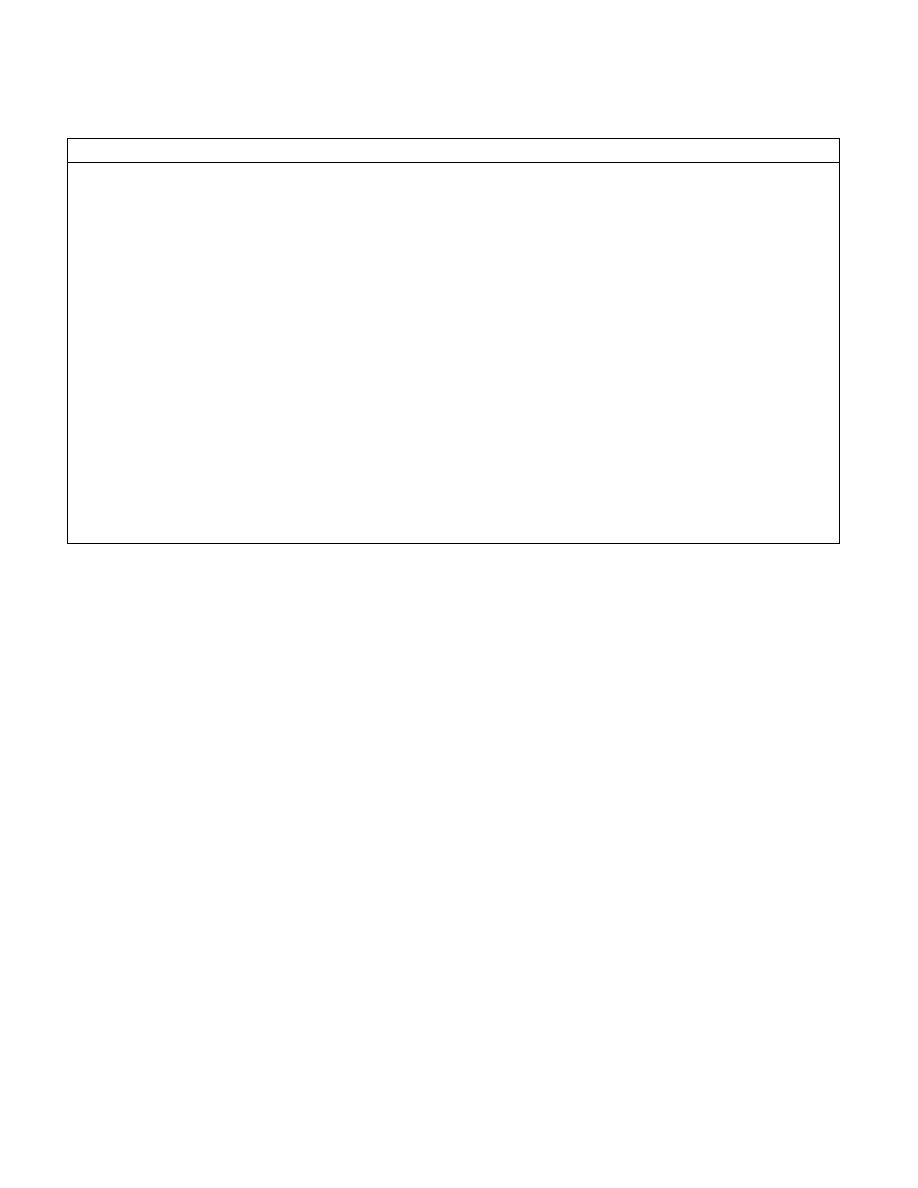

Table 36-4. Algorithm to Manage Intel PT ToPA PMI and XSAVES/XRSTORS

Pseudo Code Flow

IF (IA32_PERF_GLOBAL_STATUS.ToPA)

Save IA32_RTIT_CTL value;

IF ( IA32_RTIT_CTL.TraceEN )

Disable Intel PT by clearing TraceEn;

FI;

IF ( there is space available to grow the current ToPA table )

Add one or more ToPA entries after the last entry in the ToPA table;

Point new ToPA entry address field(s) to new output region base(s);

ELSE

Modify an upcoming ToPA entry in the current table to have END=1;

IF (output should transition to a new ToPA table )

Point the address of the “END=1” entry of the current table to the new table base;

ELSE

/* Continue to use the current ToPA table, make a circular. */

Point the address of the “END=1”l entry to the base of the current table;

Modify the ToPA entry address fields for filled output regions to point to new, unused output regions;

/* Filled regions are those with index in the range of 0 to (IA32_RTIT_MASK_PTRS.MaskOrTableOffset -1). */

FI;

FI;

Restore saved IA32_RTIT_CTL.value;

FI;