36-48 Vol. 3C

INTEL® PROCESSOR TRACE

36.4.2.9 TraceStop Packet

36.4.2.10 Core:Bus Ratio (CBR) Packet

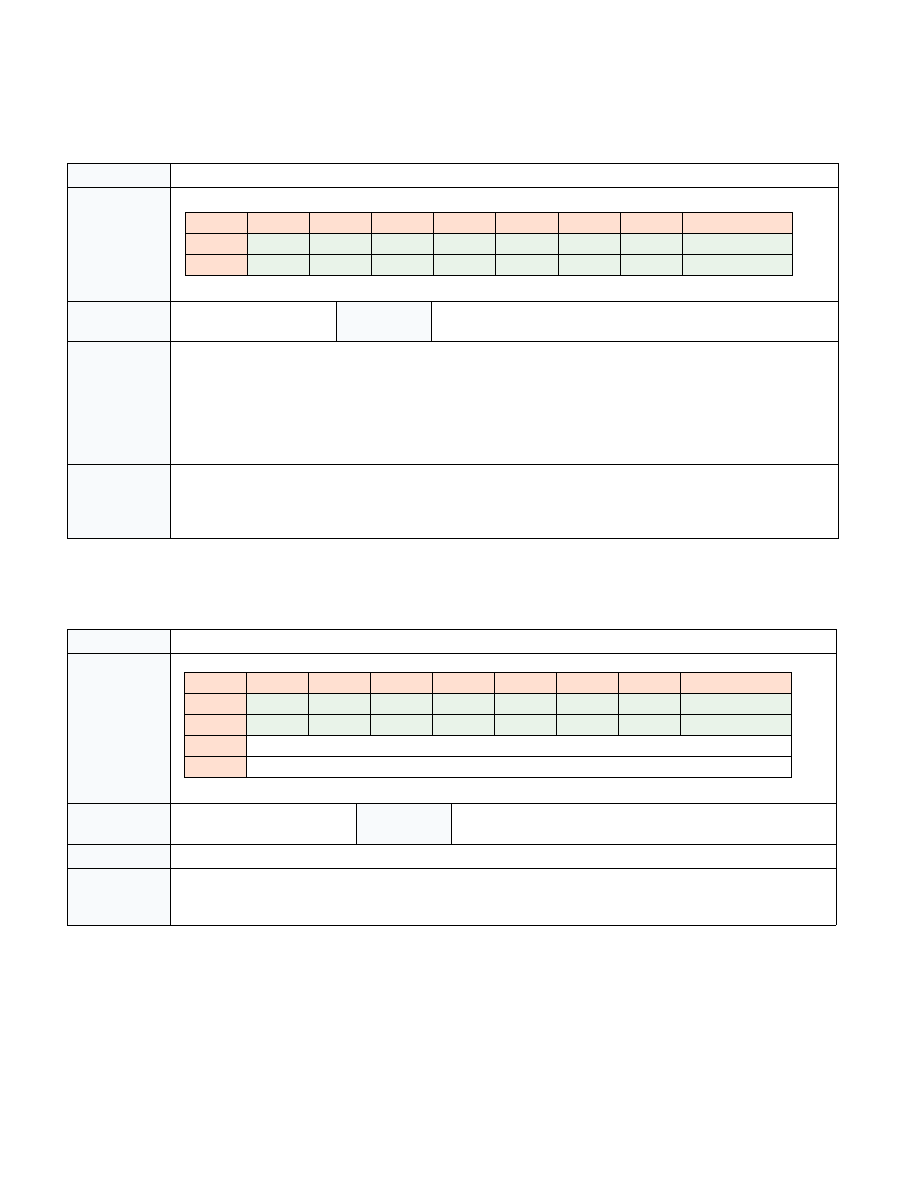

Table 36-28. TraceStop Packet Definition

Name

TraceStop Packet

Packet Format

Dependencies

TriggerEn && ContextEn

Generation

Scenario

Taken branch with target in TraceStop IP region, MOV CR3 in TraceS-

top IP region, or WRMSR that sets TraceEn in TraceStop IP region.

Description

Indicates when software has entered a user-configured TraceStop region.

When the IP matches a TraceStop range while ContextEn and TriggerEn are set, a TraceStop action occurs. This dis-

ables tracing by setting IA32_RTIT_STATUS.Stopped, thereby clearing TriggerEn, and causes a TraceStop

packet to be generated.

The TraceStop action also forces FilterEn to 0. Note that TraceStop may not force a flush of internally buffered

packets, and thus trace packet generation should still be manually disabled by clearing IA32_RTIT_CTL.TraceEn

before examining output. See Section 36.2.4.3 for more details.

Application

.If TraceStop follows a TIP.PGD (before the next TIP.PGE), then it was triggered either by the instruction that cleared

PacketEn, or it was triggered by some later instruction that executed while FilterEn=0. In either case, the TraceStop

can be applied at the IP of the TIP.PGD (if any).

If TraceStop follows a TIP.PGE (before the next TIP.PGD), it should be applied at the last known IP.

Table 36-29. CBR Packet Definition

Name

Core:Bus Ratio (CBR) Packet

Packet Format

Dependencies

TriggerEn

Generation

Scenario

After any frequency change, on C-state wake up, PSB+, and after

enabling trace packet generation.

Description

Indicates the core:bus ratio of the processor core. Useful for correlating wall-clock time and cycle time.

Application

All packets following the CBR represent instructions that executed with the new core:bus ratio, while all preceding

packets (aside from timing packets) represent instructions that executed with the prior ratio. There is not a precise

IP provided, to which to bind the CBR packet.

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

1

0

1

1

0

0

0

0

0

1

1

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

1

1

2

Core:Bus Ratio

3

Reserved