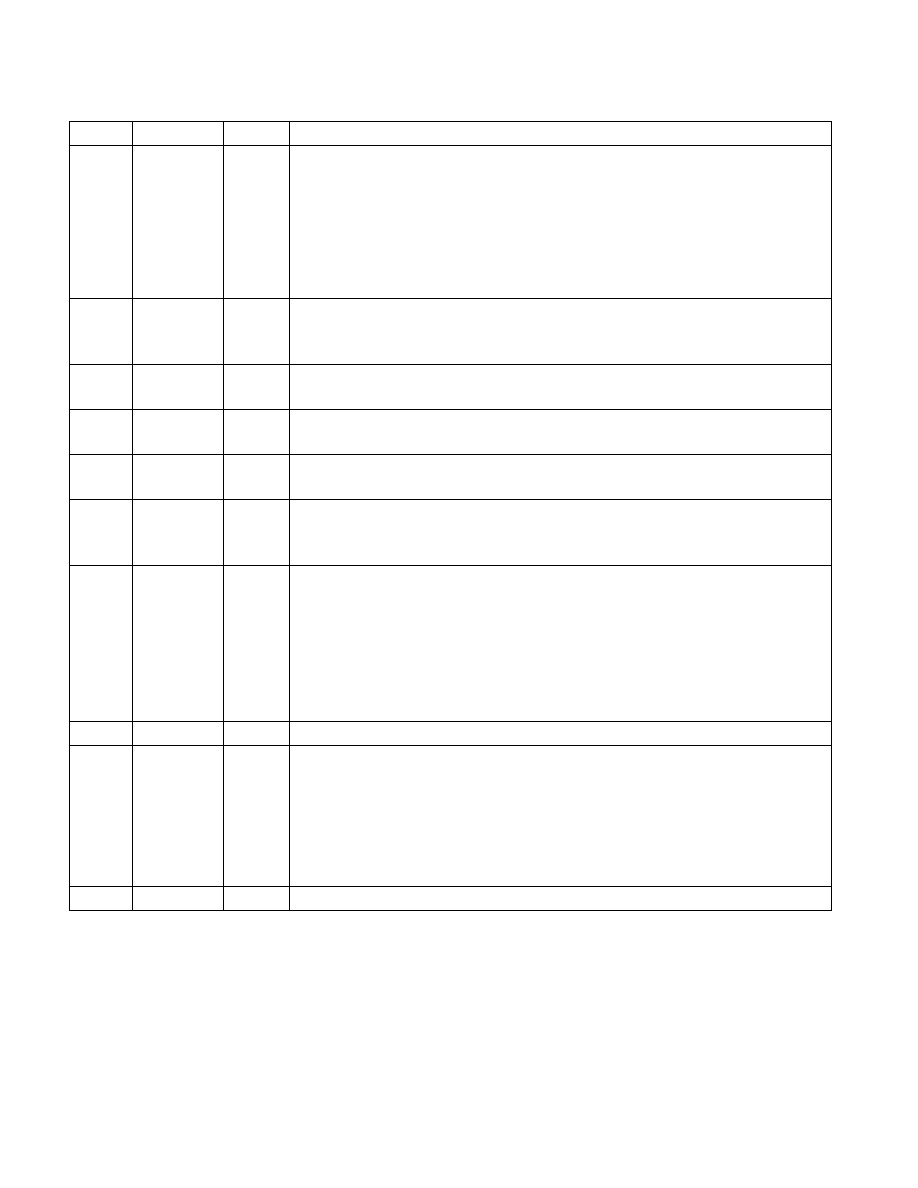

Vol. 3C 36-17

INTEL® PROCESSOR TRACE

8

ToPA

0

0: Single-range output scheme enabled if CPUID.(EAX=14H, ECX=0):ECX.SNGLRGNOUT[bit 2]

= 1 and IA32_RTIT_CTL.FabricEn=0.

1: ToPA output scheme enabled (see Section 36.2.6.2) if CPUID.(EAX=14H,

ECX=0):ECX.TOPA[bit 0] = 1, and IA32_RTIT_CTL.FabricEn=0.

Note: WRMSR to IA32_RTIT_CTL that sets TraceEn but clears this bit and FabricEn would

cause #GP, if CPUID.(EAX=14H, ECX=0):ECX.SNGLRGNOUT[bit 2] = 0.

WRMSR to IA32_RTIT_CTL that sets this bit causes #GP, if CPUID.(EAX=14H,

ECX=0):ECX.TOPA[bit 0] = 0.

9

MTCEn

0

0: Disables MTC Packet (see Section 36.4.2.16).

1: Enables MTC Packet.

This bit is reserved if CPUID.(EAX=14H, ECX=0):EBX.MTC[bit 3] = 0.

10

TSCEn

0

0: Disable TSC packets.

1: Enable TSC packets (see Section 36.4.2.11).

11

DisRETC

0

0: Enable RET compression.

1: Disable RET compression (see Section 36.2.1.2).

12

PTWEn

0

0: PTWRITE packet generation disabled.

1: PTWRITE packet generation enabled (see Table 36-40 “PTW Packet Definition”).

13

BranchEn

0

0: Disable COFI-based packets.

1: Enable COFI-based packets: FUP, TIP, TIP.PGE, TIP.PGD, TNT, MODE.Exec, MODE.TSX.

see Section 36.2.6 for details on BranchEn.

17:14

MTCFreq

0

Defines MTC packet Frequency, which is based on the core crystal clock, or Always Running

Timer (ART). MTC will be sent each time the selected ART bit toggles. The following Encodings

are defined:

0: ART(0), 1: ART(1), 2: ART(2), 3: ART(3), 4: ART(4), 5: ART(5), 6: ART(6), 7: ART(7),

8: ART(8), 9: ART(9), 10: ART(10), 11: ART(11), 12: ART(12), 13: ART(13), 14: ART(14), 15:

ART(15)

Software must use CPUID to query the supported encodings in the processor, see Section

36.3.1. Use of unsupported encodings will result in a #GP fault. This field is reserved if

CPUID.(EAX=14H, ECX=0):EBX.MTC[bit 3] = 0.

18

Reserved

0

Must be 0.

22:19

CycThresh

0

CYC packet threshold, see Section 36.3.6 for details. CYC packets will be sent with the first

eligible packet after N cycles have passed since the last CYC packet. If CycThresh is 0 then

N=0, otherwise N is defined as 2

(CycThresh-1)

. The following Encodings are defined:

0: 0, 1: 1,

2: 2,

3: 4,

4: 8,

5: 16,

6: 32,

7: 64,

8: 128, 9: 256, 10: 512,

11: 1024, 12: 2048, 13: 4096, 14: 8192, 15: 16384

Software must use CPUID to query the supported encodings in the processor, see Section

36.3.1. Use of unsupported encodings will result in a #GP fault. This field is reserved if

CPUID.(EAX=14H, ECX=0):EBX.CPSB_CAM[bit 1] = 0.

23

Reserved

0

Must be 0.

Table 36-6. IA32_RTIT_CTL MSR (Contd.)

Position

Bit Name

At Reset

Bit Description