Vol. 3C 36-49

INTEL® PROCESSOR TRACE

36.4.2.11 Timestamp Counter (TSC) Packet

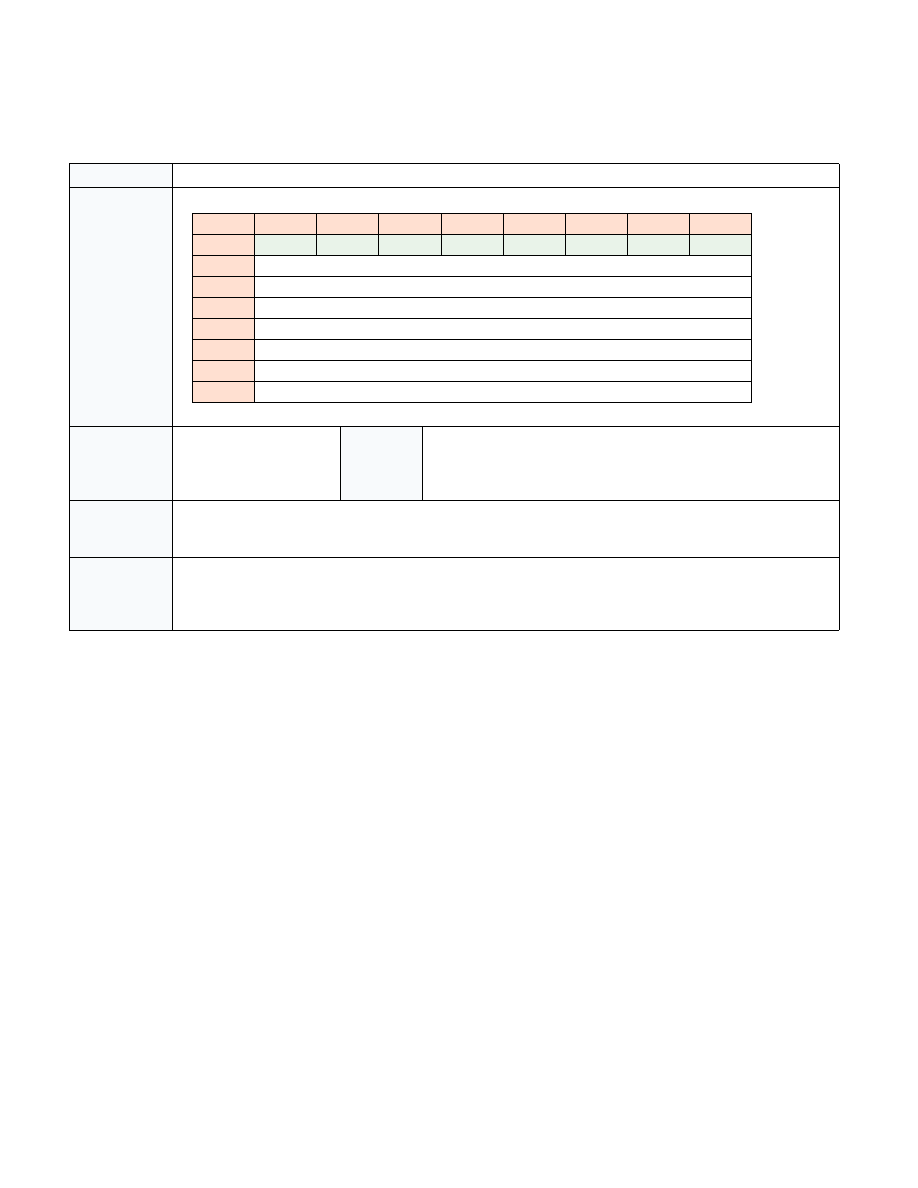

Table 36-30. TSC Packet Definition

Name

Timestamp Counter (TSC) Packet

Packet Format

Dependencies

IA32_RTIT_CTL.TSCEn &&

TriggerEn

Generation

Scenario

Sent after any event that causes the processor clocks or Intel PT timing

packets (such as MTC or CYC) to stop, This may include P-state changes,

wake from C-state, or clock modulation. Also on transition of TraceEn

from 0 to 1.

Description

When enabled by software, a TSC packet provides the lower 7 bytes of the current TSC value, as returned by the

RDTSC instruction. This may be useful for tracking wall-clock time, and synchronizing the packets in the log with

other timestamped logs.

Application

TSC packet provides a wall-clock proxy of the event which generated it (packet generation enable, sleep state wake,

etc). In all cases, TSC does not precisely indicate the time of any control flow packets; however, all preceding packets

represent instructions that executed before the indicated TSC time, and all subsequent packets represent instruc-

tions that executed after it. There is not a precise IP to which to bind the TSC packet.

7

6

5

4

3

2

1

0

0

0

0

0

1

1

0

0

1

1

SW TSC[7:0]

2

SW TSC[15:8]

3

SW TSC[23:16]

4

SW TSC[31:24]

5

SW TSC[39:32]

6

SW TSC[47:40]

7

SW TSC[55:48]