Vol. 3C 36-15

INTEL® PROCESSOR TRACE

In all cases, the error will be logged by setting IA32_RTIT_STATUS.Error, thereby disabling tracing when the prob-

lematic ToPA entry is reached (when proc_trace_table_offset points to the entry containing the error). Any packet

bytes that are internally buffered when the error is detected may be lost.

Note that operational errors may also be signaled due to attempts to access restricted memory. See Section

36.2.6.4 for details.

A tracing software have a range of flexibility using ToPA to manage the interaction of Intel PT with application

buffers, see Section 36.5.

36.2.6.3 Trace Transport Subsystem

When IA32_RTIT_CTL.FabricEn is set, the IA32_RTIT_CTL.ToPA bit is ignored, and trace output is written to the

trace transport subsystem. The endpoints of this transport are platform-specific, and details of configuration

options should refer to the specific platform documentation. The FabricEn bit is available to be set if

CPUID(EAX=14H,ECX=0):EBX[bit 3] = 1.

36.2.6.4 Restricted Memory Access

Packet output cannot be directed to any regions of memory that are restricted by the platform. In particular, all

memory accesses on behalf of packet output are checked against the SMRR regions. If there is any overlap with

these regions, trace data collection will not function properly. Exact processor behavior is implementation-depen-

dent; Table 36-5 summarizes several scenarios.

It should also be noted that packet output should not be routed to the 4KB APIC MMIO region, as defined by the

IA32_APIC_BASE MSR. For details about the APIC, refer to Intel® 64 and IA-32 Architectures Software Devel-

oper’s Manual, Volume 3A. No error is signaled for this case.

Modifications to Restricted Memory Regions

It is recommended that software disable packet generation before modifying the SMRRs to change the scope of the

SMRR regions. This is because the processor reserves the right to cache any number of ToPA table entries inter-

nally, after checking them against restricted memory ranges. Once cached, the entries will not be checked again,

meaning one could potentially route packet output to a newly restricted region. Software can ensure that any

cached entries are written to memory by clearing IA32_RTIT_CTL.TraceEn.

36.2.7

Enabling and Configuration MSRs

36.2.7.1 General Considerations

Trace packet generation is enabled and configured by a collection of model-specific registers (MSRs), which are

detailed below. Some notes on the configuration MSR behavior:

•

If Intel Processor Trace is not supported by the processor (see Section 36.3.1), RDMSR or WRMSR of the

IA32_RTIT_* MSRs will cause #GP.

•

A WRMSR to any of these configuration MSRs that begins and ends with IA32_RTIT_CTL.TraceEn set will #GP

fault. Packet generation must be disabled before the configuration MSRs can be changed.

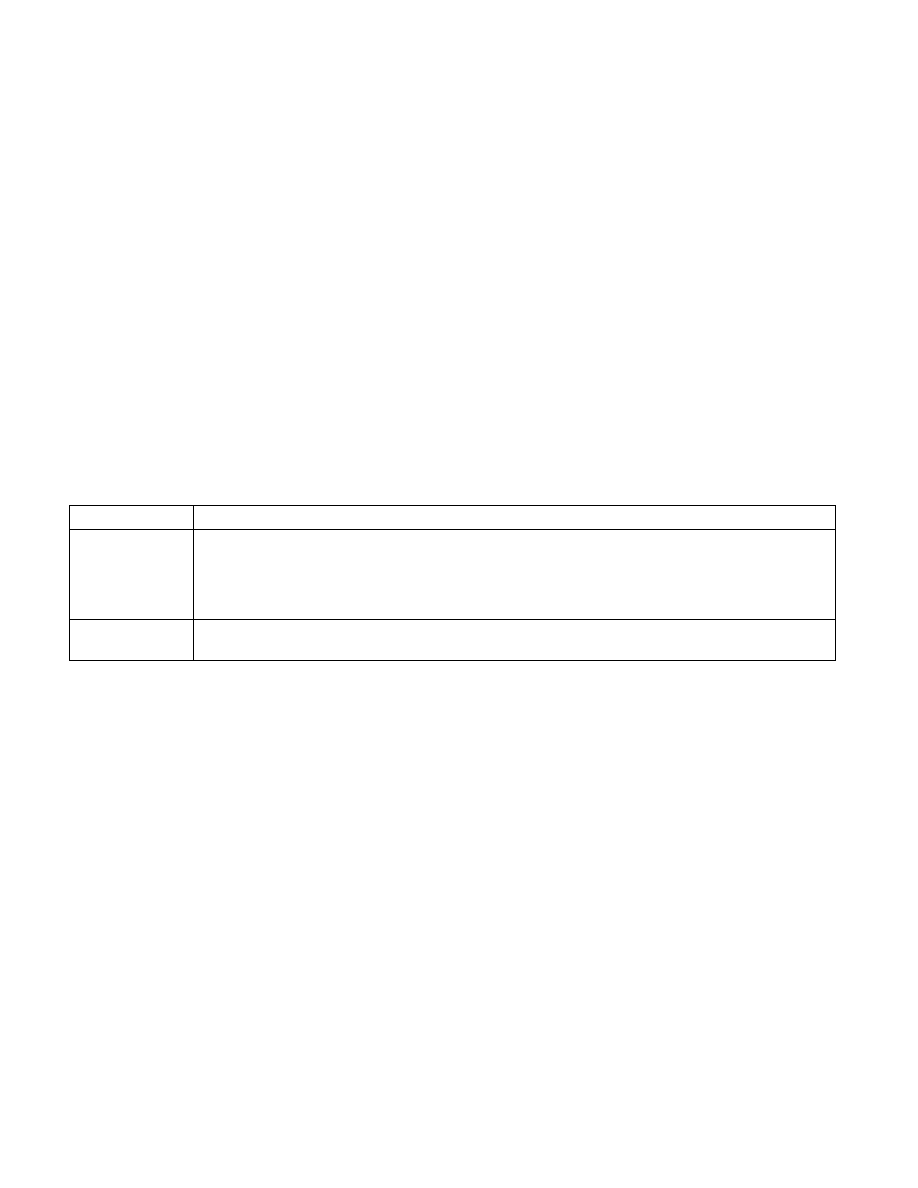

Table 36-5. Behavior on Restricted Memory Access

Scenario

Description

ToPA output region

overlaps with

SMRR

Stores to the restricted memory region will be dropped, and that packet data will be lost. Any attempt to read

from that restricted region will return all 1s. The processor also may signal an error (Section 36.3.9) and disable

tracing when the output pointer reaches the restricted region. If packet generation remains enabled, then

packet output may continue once stores are no longer directed to restricted memory (on wrap, or if the output

region is larger than the restricted memory region).

ToPA table overlaps

with SMRR

The processor will signal an error (Section 36.3.9) and disable tracing when the ToPA read pointer

(IA32_RTIT_OUTPUT_BASE + (proc_trace_table_offset « 3)) enters the restricted region.