Vol. 3C 36-61

INTEL® PROCESSOR TRACE

36.4.2.25 Power Exit (PWRX) Packet

36.5

TRACING IN VMX OPERATION

On processors that IA32_VMX_MISC[bit 14] reports 1, TraceEn can be set in VMX operation. A series of mecha-

nisms exist to allow the VMM to configure tracing based on the desired trace domain, and on the consumer of the

trace output. The VMM can configure specific VM-execution controls to control what virtualization-specific data are

included within the trace packets (see Section 36.5.1 for details). MSR save and load lists can be employed by the

VMM to restrict tracing to the desired context (see Section 36.5.2 for details). These configuration options are

summarized in Table 36-45. Table 36-45 covers common Intel PT usages while SMIs are handled by the default

SMM treatment. Tracing with SMM Transfer Monitor is described in Section 36.6.

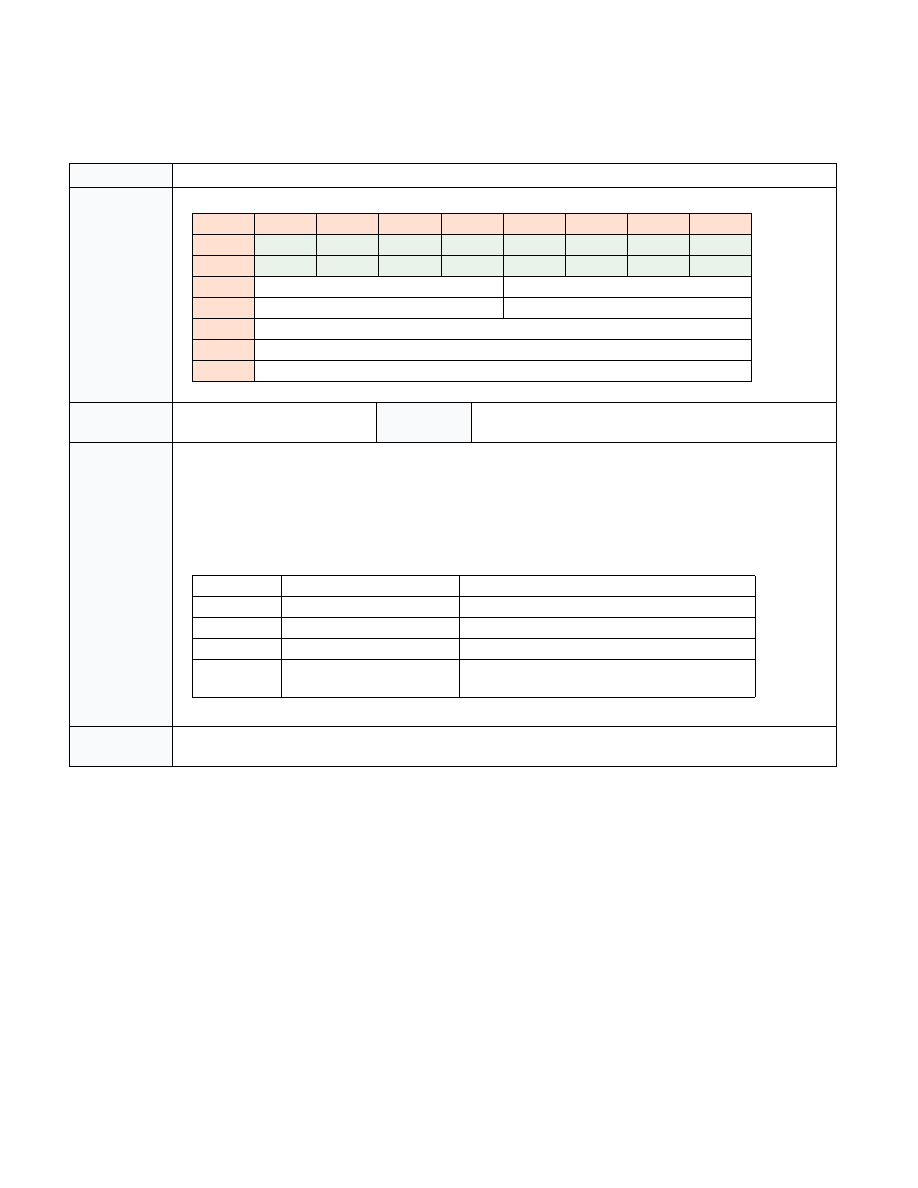

Table 36-44. PWRX Packet Definition

Name

PWRX Packet

Packet Format

Dependencies

TriggerEn & PwrEvtEn

Generation

Scenario

Transition from a C-state deeper than C0.0 to C0.

Description

Indicates processor return to thread C0 from a C-state deeper than C0.0.

The Last Core C-State field provides the MWAIT encoding for the core C-state at the time of the wake. The Deepest

Core C-State provides the MWAIT encoding for the deepest core C-state achieved during the sleep session, or since

leaving thread C0. MWAIT encodings for C-states can be found in Table 4-11 in the Intel® 64 and IA-32 Architec-

tures Software Developer’s Manual, Volume 2B. Note that these values reflect only the core C-state, and hence will

not exceed the maximum supported core C-state, even if deeper C-states can be requested.

The Wake Reason field is one-hot, encoded as follows:

Application

PWRX will always apply to the same IP as the PWRE. The time of wake can be discerned from (optional) timing pack-

ets that precede PWRX.

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

1

0

1

1

0

1

0

0

0

1

0

2

Last Core C-State

Deepest Core C-State

3

Reserved

Wake Reason

4

Reserved

5

Reserved

6

Reserved

Bit

Field

Meaning

0

Interrupt

Wake due to external interrupt received.

1

Reserved

2

Store to Monitored Address

Wake due to store to monitored address.

3

HW Wake

Wake due to hardware autonomous condition,

such as HDC.