36-10 Vol. 3C

INTEL® PROCESSOR TRACE

IA32_RTIT_OUTPUT_MASK_PTRS. While tracing is enabled, the processor updates

IA32_RTIT_OUTPUT_MASK_PTRS.OutputOffset with changes to proc_trace_output_offset, but these updates

may not be synchronous to software execution. When tracing is disabled, the processor ensures that the MSR

contains the latest value of proc_trace_output_offset.

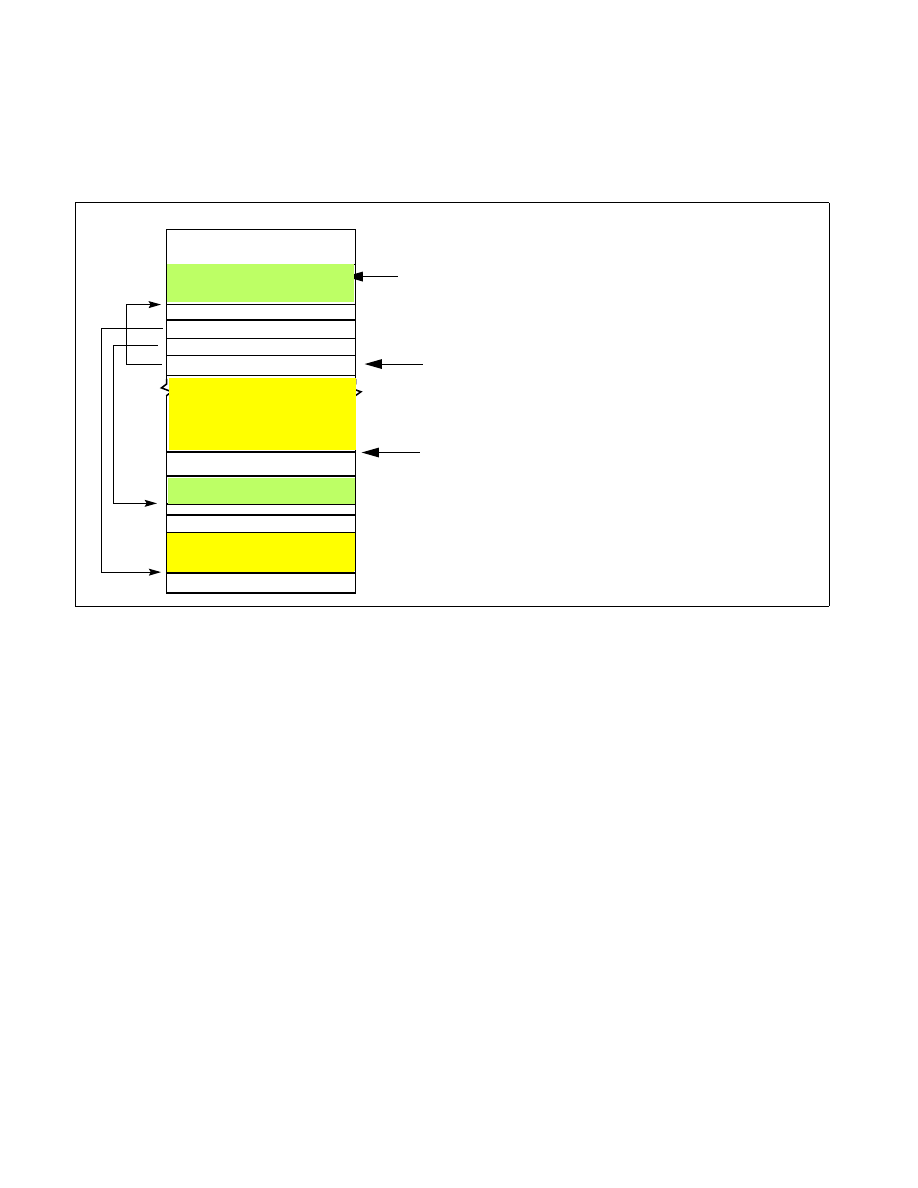

Figure 36-1 provides an illustration (not to scale) of the table and associated pointers.

With the ToPA mechanism, the processor writes packets to the current output region (identified by

proc_trace_table_base and the proc_trace_table_offset). The offset within that region to which the next byte will

be written is identified by proc_trace_output_offset. When that region is filled with packet output (thus

proc_trace_output_offset = RegionSize–1), proc_trace_table_offset is moved to the next ToPA entry,

proc_trace_output_offset is set to 0, and packet writes begin filling the new output region specified by

proc_trace_table_offset.

As packets are written out, each store derives its physical address as follows:

trace_store_phys_addr

Base address from current ToPA table entry +

proc_trace_output_offset

Eventually, the regions represented by all entries in the table may become full, and the final entry of the table is

reached. An entry can be identified as the final entry because it has either the END or STOP attribute. The END

attribute indicates that the address in the entry does not point to another output region, but rather to another ToPA

table. The STOP attribute indicates that tracing will be disabled once the corresponding region is filled. See Section

36.2.6.2 for details on STOP.

When an END entry is reached, the processor loads proc_trace_table_base with the base address held in this END

entry, thereby moving the current table pointer to this new table. The proc_trace_table_offset is reset to 0, as is

the proc_trace_output_offset, and packet writes will resume at the base address indicated in the first entry.

If the table has no STOP or END entry, and trace-packet generation remains enabled, eventually the maximum

table size will be reached (proc_trace_table_offset = FFFFFFFFH). In this case, the proc_trace_table_offset and

proc_trace_output_offset are reset to 0 (wrapping back to the beginning of the current table) once the last output

region is filled.

Figure 36-1. ToPA Memory Illustration

0FF_FFFF _FFFFH

STOP=1

proc_trace_output_offset: IA32_RTIT_OUTPUT_MASK_PTRS.OutputOffset

proc_trace_table_offset: IA32_RTIT_OUTPUT_MASK_PTRS.TableOffset

proc_trace_table_base: IA32_RTIT_OUTPUT_BASE

0

ToPA Table B

Physical Memory

64K

OutputBaseX

4K

OutputBaseY

END=1

TableBaseB

ToPA Table A

OutputRegionY

OutputRegionX