35-320 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

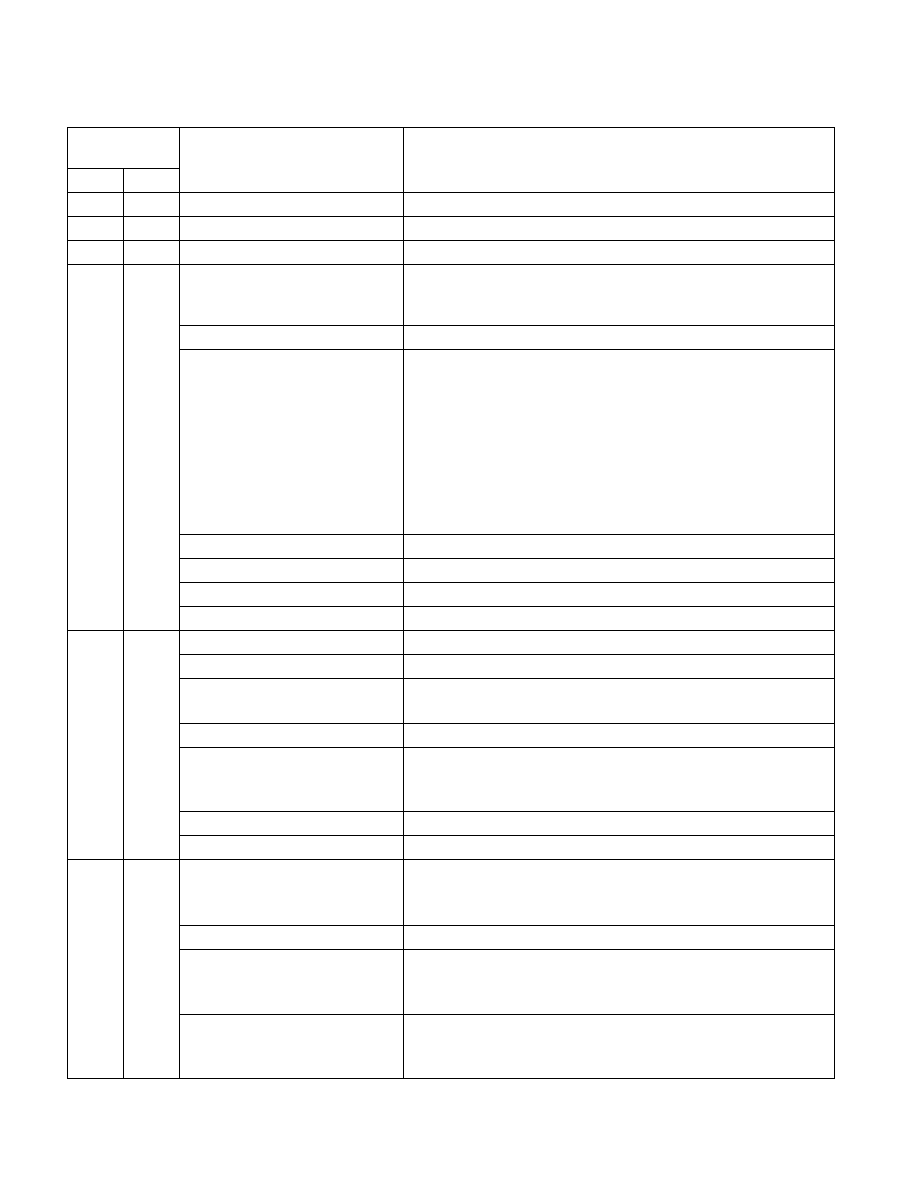

Table 35-46. MSRs in the P6 Family Processors

Register

Address

Register Name

Bit Description

Hex

Dec

0H

0

P5_MC_ADDR

See Section 35.22, “MSRs in Pentium Processors.”

1H

1

P5_MC_TYPE

See Section 35.22, “MSRs in Pentium Processors.”

10H

16

TSC

See Section 17.15, “Time-Stamp Counter.”

17H

23

IA32_PLATFORM_ID

Platform ID (R)

The operating system can use this MSR to determine “slot” information for

the processor and the proper microcode update to load.

49:0

Reserved.

52:50

Platform Id (R)

Contains information concerning the intended platform for the processor.

52 51 50

0 0 0 Processor

Flag

0

0 0 1 Processor

Flag

1

0 1 0 Processor

Flag

2

0 1 1 Processor

Flag

3

1 0 0 Processor

Flag

4

1 0 1 Processor

Flag

5

1 1 0 Processor

Flag

6

1 1 1 Processor

Flag

7

56:53

L2 Cache Latency Read.

59:57

Reserved.

60

Clock Frequency Ratio Read.

63:61

Reserved.

1BH

27

APIC_BASE

Section 10.4.4, “Local APIC Status and Location.”

7:0

Reserved.

8

Boot Strap Processor indicator Bit

1 = BSP

10:9

Reserved.

11

APIC Global Enable Bit - Permanent till reset

1 = Enabled

0 = Disabled

31:12

APIC Base Address.

63:32

Reserved.

2AH

42

EBL_CR_POWERON

Processor Hard Power-On Configuration

(R/W) Enables and disables processor features;

(R) indicates current processor configuration.

0

Reserved.1

1

Data Error Checking Enable (R/W)

1 = Enabled

0 = Disabled

2

Response Error Checking Enable FRCERR Observation Enable (R/W)

1 = Enabled

0 = Disabled