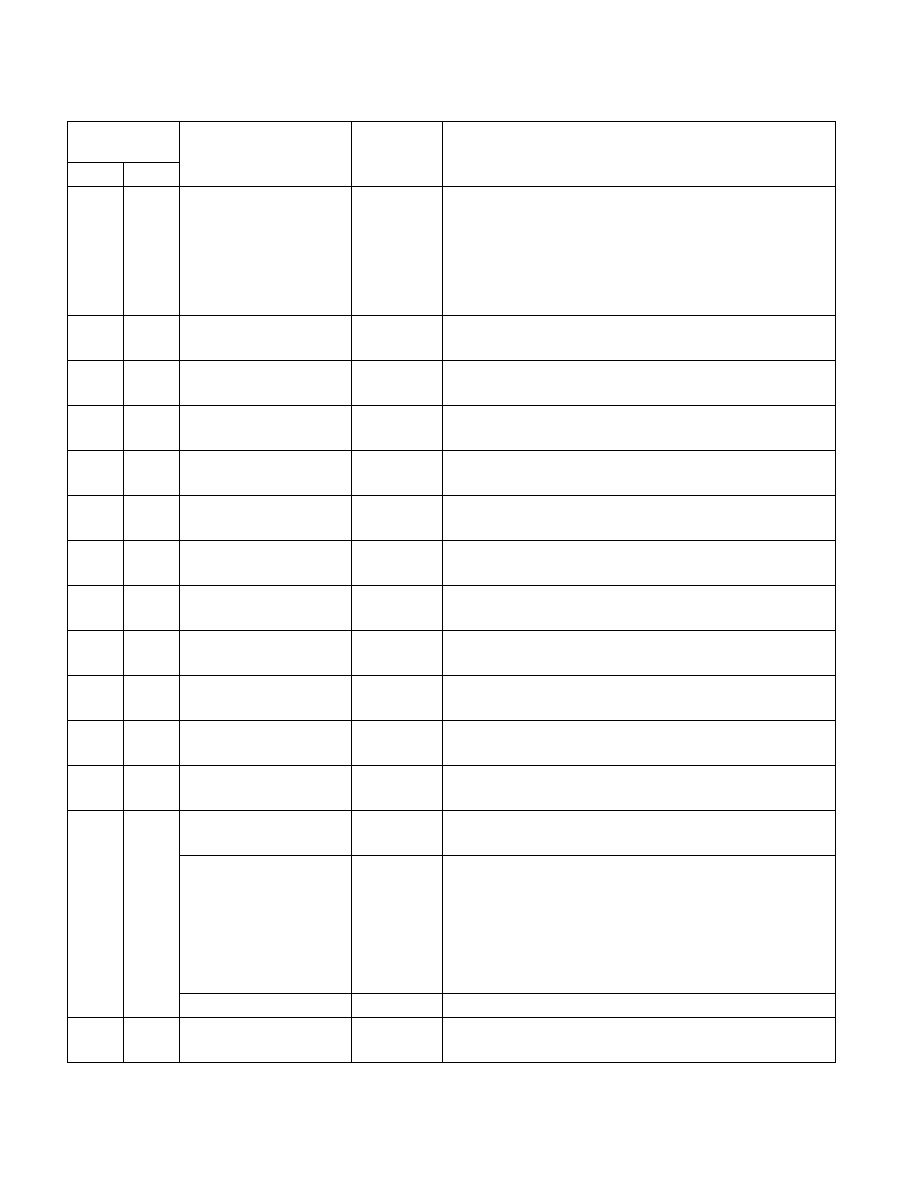

35-306 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

40H

64

MSR_LASTBRANCH_0

Unique

Last Branch Record 0 (R/W)

One of 8 last branch record registers on the last branch record

stack: bits 31-0 hold the ‘from’ address and bits 63-32 hold the ‘to’

address. See also:

• Last Branch Record Stack TOS at 1C9H

• Section 17.13, “Last Branch, Interrupt, and Exception Recording

41H

65

MSR_LASTBRANCH_1

Unique

Last Branch Record 1 (R/W)

See description of MSR_LASTBRANCH_0.

42H

66

MSR_LASTBRANCH_2

Unique

Last Branch Record 2 (R/W)

See description of MSR_LASTBRANCH_0.

43H

67

MSR_LASTBRANCH_3

Unique

Last Branch Record 3 (R/W)

See description of MSR_LASTBRANCH_0.

44H

68

MSR_LASTBRANCH_4

Unique

Last Branch Record 4 (R/W)

See description of MSR_LASTBRANCH_0.

45H

69

MSR_LASTBRANCH_5

Unique

Last Branch Record 5 (R/W)

See description of MSR_LASTBRANCH_0.

46H

70

MSR_LASTBRANCH_6

Unique

Last Branch Record 6 (R/W)

See description of MSR_LASTBRANCH_0.

47H

71

MSR_LASTBRANCH_7

Unique

Last Branch Record 7 (R/W)

See description of MSR_LASTBRANCH_0.

79H

121

IA32_BIOS_UPDT_TRIG

Unique

BIOS Update Trigger Register (W)

See Table 35-2.

8BH

139

IA32_BIOS_SIGN_ID

Unique

BIOS Update Signature ID (RO)

See Table 35-2.

C1H

193

IA32_PMC0

Unique

Performance counter register

See Table 35-2.

C2H

194

IA32_PMC1

Unique

Performance counter register

See Table 35-2.

CDH

205

MSR_FSB_FREQ

Shared

Scaleable Bus Speed (RO)

This field indicates the scaleable bus clock speed:

2:0

• 101B: 100 MHz (FSB 400)

• 001B: 133 MHz (FSB 533)

• 011B: 167 MHz (FSB 667)

133.33 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 101B.

166.67 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 001B.

63:3

Reserved.

E7H

231

IA32_MPERF

Unique

Maximum Performance Frequency Clock Count. (RW)

See Table 35-2.

Table 35-44. MSRs in Intel® Core™ Solo, Intel® Core™ Duo Processors, and Dual-Core Intel® Xeon® Processor LV

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec