35-302 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.18.1 MSRs Unique to Intel

®

Xeon

®

Processor MP with L3 Cache

The MSRs listed in Table 35-42 apply to Intel

®

Xeon

®

Processor MP with up to 8MB level three cache. These proces-

sors can be detected by enumerating the deterministic cache parameter leaf of CPUID instruction (with EAX = 4 as

input) to detect the presence of the third level cache, and with CPUID reporting family encoding 0FH, model

encoding 3 or 4 (see CPUID instruction for more details).

C000_

0080H

IA32_EFER

3, 4, 6

Unique

Extended Feature Enables

See Table 35-2.

C000_

0081H

IA32_STAR

3, 4, 6

Unique

System Call Target Address (R/W)

See Table 35-2.

C000_

0082H

IA32_LSTAR

3, 4, 6

Unique

IA-32e Mode System Call Target Address (R/W)

See Table 35-2.

C000_

0084H

IA32_FMASK

3, 4, 6

Unique

System Call Flag Mask (R/W)

See Table 35-2.

C000_

0100H

IA32_FS_BASE

3, 4, 6

Unique

Map of BASE Address of FS (R/W)

See Table 35-2.

C000_

0101H

IA32_GS_BASE

3, 4, 6

Unique

Map of BASE Address of GS (R/W)

See Table 35-2.

C000_

0102H

IA32_KERNEL_GSBASE

3, 4, 6

Unique

Swap Target of BASE Address of GS (R/W)

See Table 35-2.

NOTES

1. For HT-enabled processors, there may be more than one logical processors per physical unit. If an MSR is Shared, this means that

one MSR is shared between logical processors. If an MSR is unique, this means that each logical processor has its own MSR.

Table 35-42. MSRs Unique to 64-bit Intel® Xeon® Processor MP with

Up to an 8 MB L3 Cache

Register Address

Register Name

Fields and Flags

Model Avail-

ability

Shared/

Unique

Bit Description

107CCH

MSR_IFSB_BUSQ0

3, 4

Shared

IFSB BUSQ Event Control and Counter

Register (R/W)

See Section 18.17, “Performance

Monitoring on 64-bit Intel Xeon Processor

MP with Up to 8-MByte L3 Cache.”

107CDH

MSR_IFSB_BUSQ1

3, 4

Shared

IFSB BUSQ Event Control and Counter

Register (R/W)

107CEH

MSR_IFSB_SNPQ0

3, 4

Shared

IFSB SNPQ Event Control and Counter

Register (R/W)

See Section 18.17, “Performance

Monitoring on 64-bit Intel Xeon Processor

MP with Up to 8-MByte L3 Cache.”

107CFH

MSR_IFSB_SNPQ1

3, 4

Shared

IFSB SNPQ Event Control and Counter

Register (R/W)

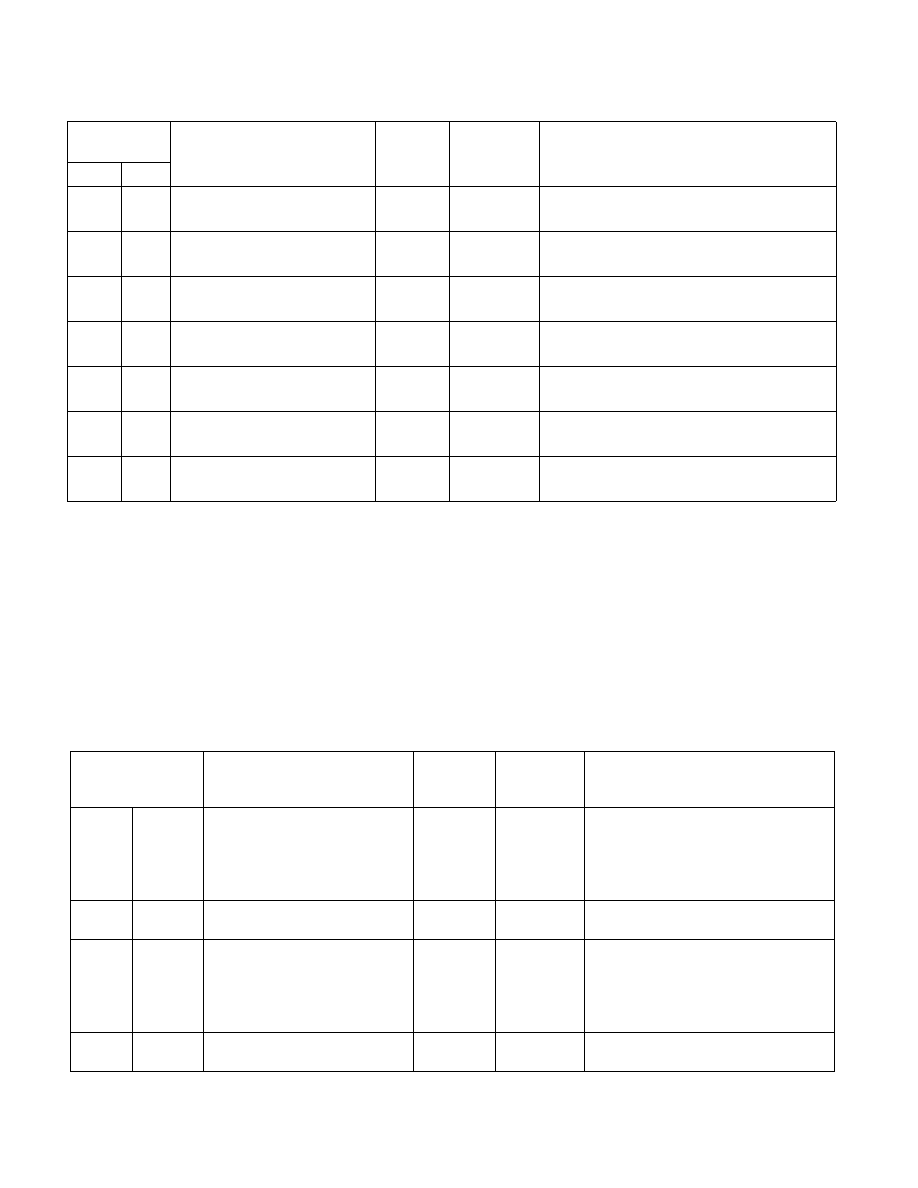

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec