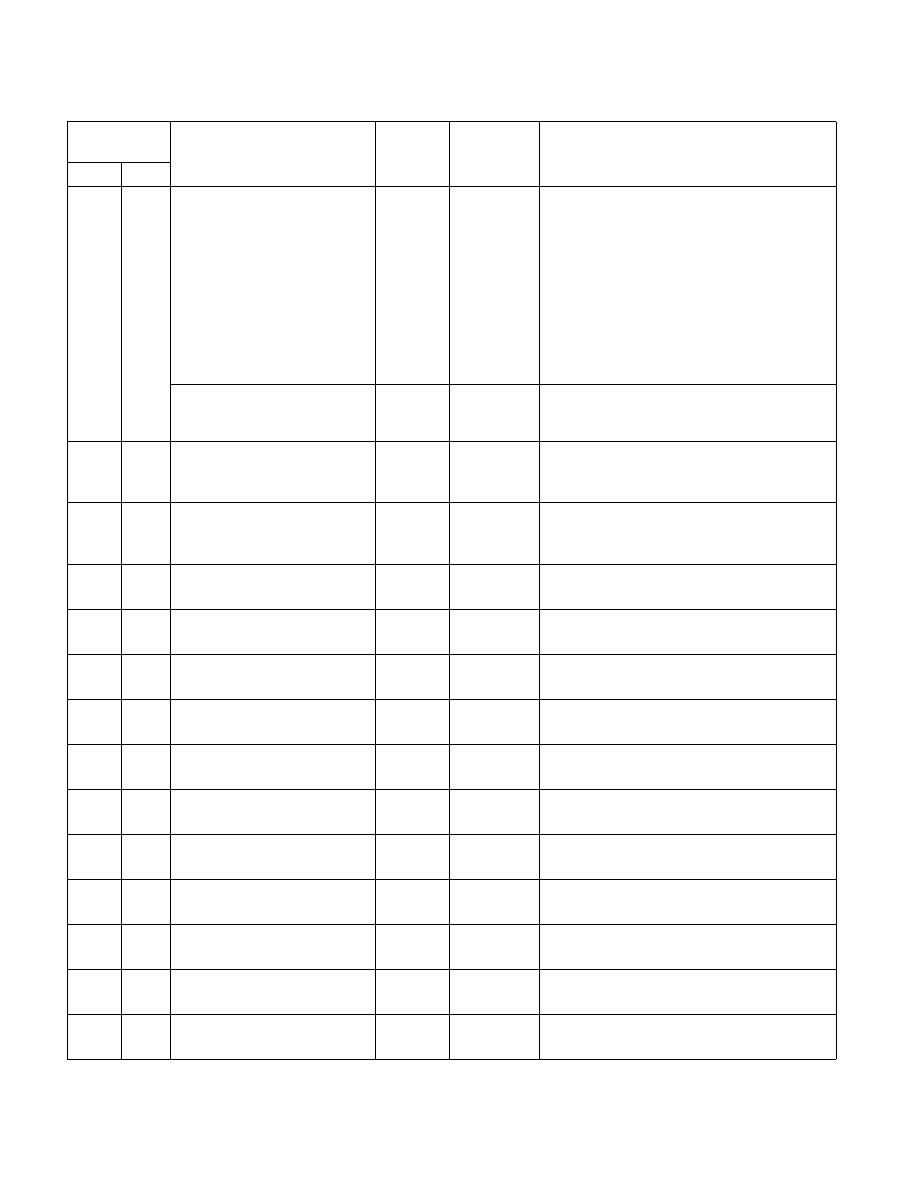

35-290 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

1DBH

475

MSR_LASTBRANCH_0

0, 1, 2

Unique

Last Branch Record 0 (R/W)

One of four last branch record registers on the last

branch record stack. It contains pointers to the

source and destination instruction for one of the

last four branches, exceptions, or interrupts that

the processor took.

MSR_LASTBRANCH_0 through

MSR_LASTBRANCH_3 at 1DBH-1DEH are

available only on family 0FH, models 0H-02H.

They have been replaced by the MSRs at 680H-

68FH and 6C0H-6CFH.

See Section 17.10, “Last Branch, Call Stack,

Interrupt, and Exception Recording for Processors

based on Skylake Microarchitecture.”

1DDH

477

MSR_LASTBRANCH_2

0, 1, 2

Unique

Last Branch Record 2

See description of the MSR_LASTBRANCH_0 MSR

at 1DBH.

1DEH

478

MSR_LASTBRANCH_3

0, 1, 2

Unique

Last Branch Record 3

See description of the MSR_LASTBRANCH_0 MSR

at 1DBH.

200H

512

IA32_MTRR_PHYSBASE0

0, 1, 2, 3,

4, 6

Shared

Variable Range Base MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

201H

513

IA32_MTRR_PHYSMASK0

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

202H

514

IA32_MTRR_PHYSBASE1

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

203H

515

IA32_MTRR_PHYSMASK1

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

204H

516

IA32_MTRR_PHYSBASE2

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

205H

517

IA32_MTRR_PHYSMASK2

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs”.

206H

518

IA32_MTRR_PHYSBASE3

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

207H

519

IA32_MTRR_PHYSMASK3

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

208H

520

IA32_MTRR_PHYSBASE4

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

209H

521

IA32_MTRR_PHYSMASK4

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

20AH

522

IA32_MTRR_PHYSBASE5

0, 1, 2, 3,

4, 6

Shared

Variable Range Mask MTRR

See Section 11.11.2.3, “Variable Range MTRRs.”

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec