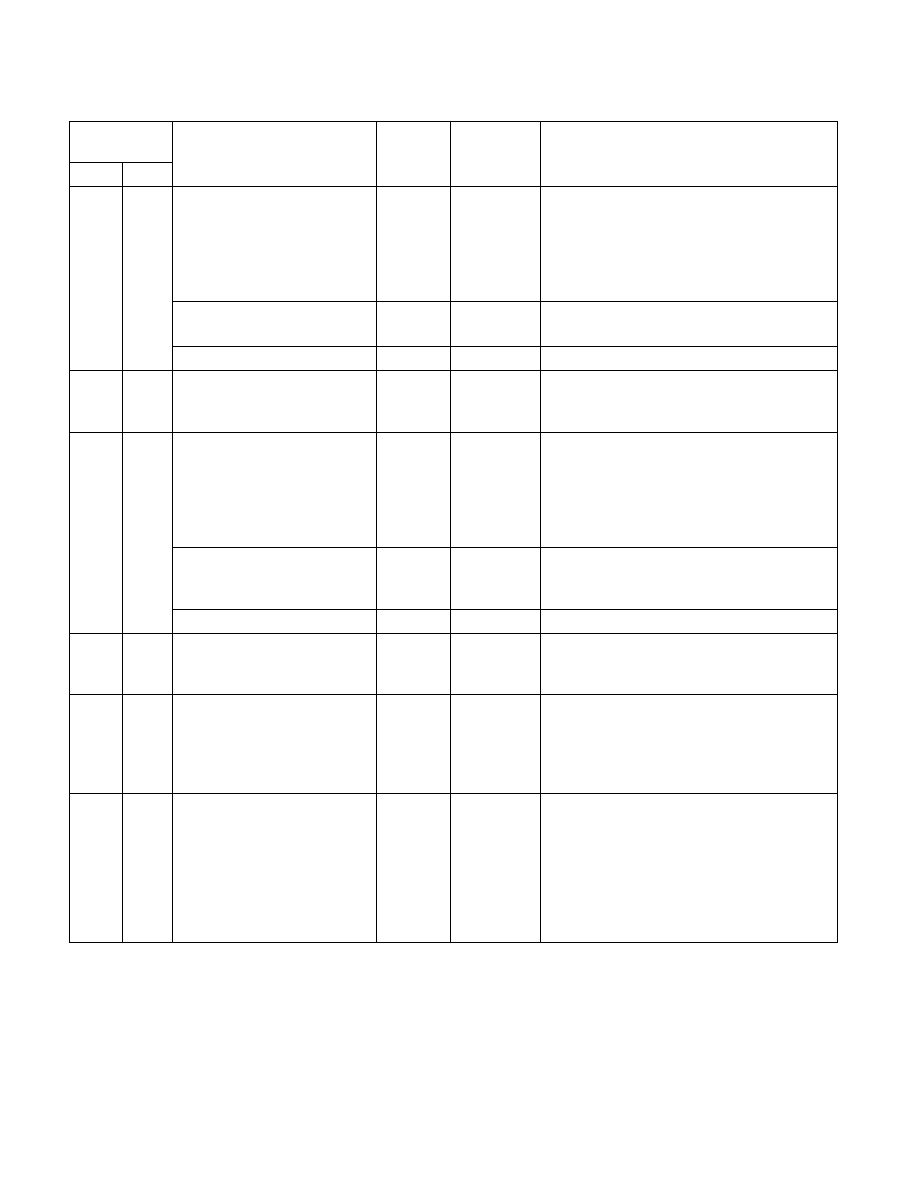

Vol. 3C 35-289

MODEL-SPECIFIC REGISTERS (MSRS)

1D7H

471

MSR_LER_FROM_LIP

0, 1, 2, 3,

4, 6

Unique

Last Exception Record From Linear IP (R)

Contains a pointer to the last branch instruction

that the processor executed prior to the last

exception that was generated or the last interrupt

that was handled.

See Section 17.11.3, “Last Exception Records.”

31:0

From Linear IP

Linear address of the last branch instruction.

63:32

Reserved.

1D7H

471

63:0

Unique

From Linear IP

Linear address of the last branch instruction (If IA-

32e mode is active).

1D8H

472

MSR_LER_TO_LIP

0, 1, 2, 3,

4, 6

Unique

Last Exception Record To Linear IP (R)

This area contains a pointer to the target of the

last branch instruction that the processor

executed prior to the last exception that was

generated or the last interrupt that was handled.

See Section 17.11.3, “Last Exception Records.”

31:0

From Linear IP

Linear address of the target of the last branch

instruction.

63:32

Reserved.

1D8H

472

63:0

Unique

From Linear IP

Linear address of the target of the last branch

instruction (If IA-32e mode is active).

1D9H

473

MSR_DEBUGCTLA

0, 1, 2, 3,

4, 6

Unique

Debug Control (R/W)

Controls how several debug features are used. Bit

definitions are discussed in the referenced

section.

See Section 17.11.1, “MSR_DEBUGCTLA MSR.”

1DAH

474

MSR_LASTBRANCH

_TOS

0, 1, 2, 3,

4, 6

Unique

Last Branch Record Stack TOS (R/W)

Contains an index (0-3 or 0-15) that points to the

top of the last branch record stack (that is, that

points the index of the MSR containing the most

recent branch record).

See Section 17.11.2, “LBR Stack for Processors

Based on Intel NetBurst® Microarchitecture”; and

addresses 1DBH-1DEH and 680H-68FH.

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec