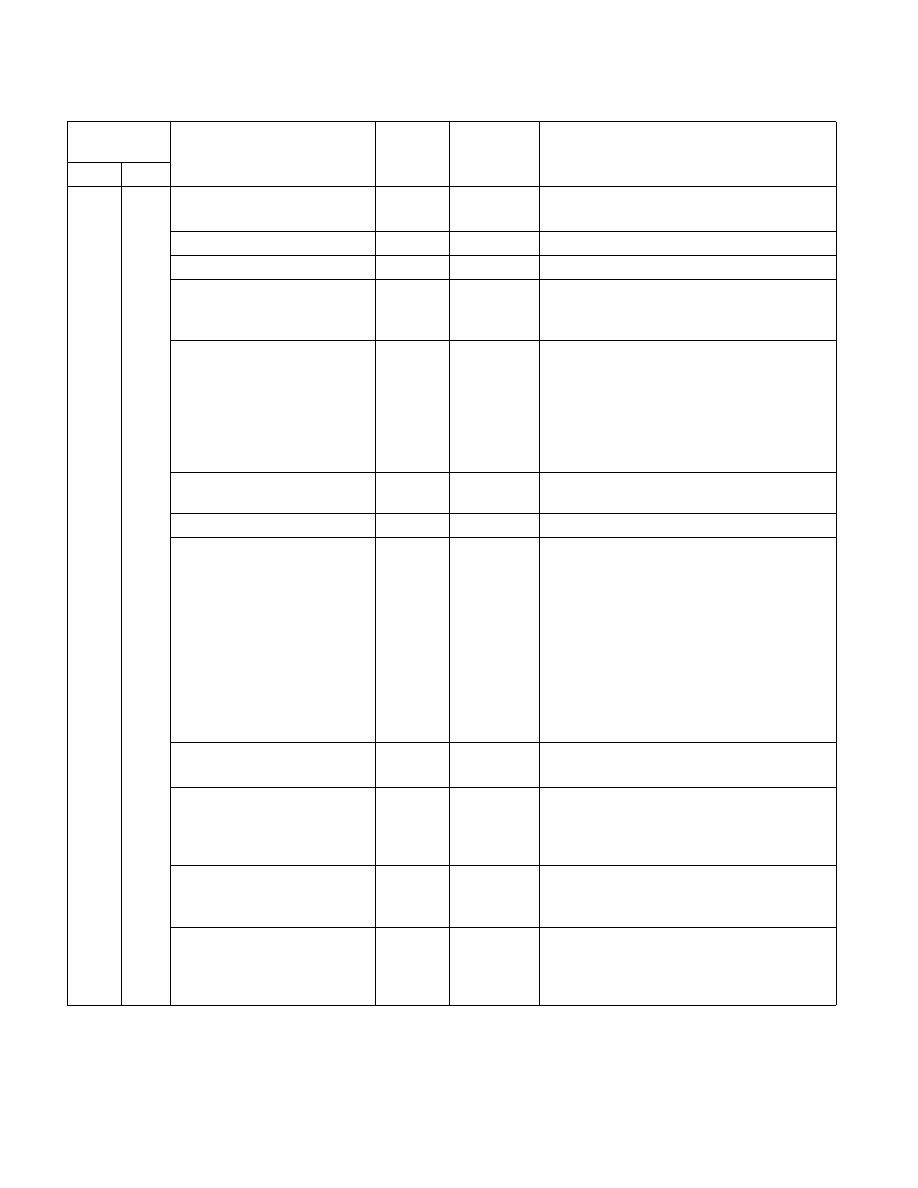

35-286 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

0

Fast-Strings Enable. See Table 35-2.

1

Reserved.

2

x87 FPU Fopcode Compatibility Mode Enable

3

Thermal Monitor 1 Enable

See Section 14.7.2, “Thermal Monitor,” and see

4

Split-Lock Disable

When set, the bit causes an #AC exception to be

issued instead of a split-lock cycle. Operating

systems that set this bit must align system

structures to avoid split-lock scenarios.

When the bit is clear (default), normal split-locks

are issued to the bus.

This debug feature is specific to the Pentium 4

processor.

5

Reserved.

6

Third-Level Cache Disable (R/W)

When set, the third-level cache is disabled; when

clear (default) the third-level cache is enabled.

This flag is reserved for processors that do not

have a third-level cache.

Note that the bit controls only the third-level

cache; and only if overall caching is enabled

through the CD flag of control register CR0, the

page-level cache controls, and/or the MTRRs.

See Section 11.5.4, “Disabling and Enabling the L3

7

Performance Monitoring Available (R)

See Table 35-2.

8

Suppress Lock Enable

When set, assertion of LOCK on the bus is

suppressed during a Split Lock access. When clear

(default), LOCK is not suppressed.

9

Prefetch Queue Disable

When set, disables the prefetch queue. When clear

(default), enables the prefetch queue.

10

FERR# Interrupt Reporting Enable (R/W)

When set, interrupt reporting through the FERR#

pin is enabled; when clear, this interrupt reporting

function is disabled.

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec