Vol. 3C 35-281

MODEL-SPECIFIC REGISTERS (MSRS)

31:24

Core Clock Frequency to System Bus

Frequency Ratio (R)

The processor core clock frequency to system bus

frequency ratio observed at the de-assertion of

the reset pin.

63:25

Reserved.

2CH

44

MSR_EBC_FREQUENCY_ID

0, 1

Shared

Processor Frequency Configuration (R)

The bit field layout of this MSR varies according to

the MODEL value of the CPUID version

information. This bit field layout applies to

Pentium 4 and Xeon Processors with MODEL

encoding less than 2.

Indicates current processor frequency

configuration.

20:0

Reserved.

23:21

Scalable Bus Speed (R/W)

Indicates the intended scalable bus speed:

Encoding Scalable Bus Speed

000B

100 MHz

All others values reserved.

63:24

Reserved.

3AH

58

IA32_FEATURE_CONTROL

3, 4, 6

Unique

Control Features in IA-32 Processor (R/W)

See Table 35-2

(If CPUID.01H:ECX.[bit 5])

79H

121

IA32_BIOS_UPDT_TRIG

0, 1, 2, 3,

4, 6

Shared

BIOS Update Trigger Register (W)

See Table 35-2.

8BH

139

IA32_BIOS_SIGN_ID

0, 1, 2, 3,

4, 6

Unique

BIOS Update Signature ID (R/W)

See Table 35-2.

9BH

155

IA32_SMM_MONITOR_CTL

3, 4, 6

Unique

SMM Monitor Configuration (R/W)

See Table 35-2.

FEH

254

IA32_MTRRCAP

0, 1, 2, 3,

4, 6

Unique

MTRR Information

See Section 11.11.1, “MTRR Feature

174H

372

IA32_SYSENTER_CS

0, 1, 2, 3,

4, 6

Unique

CS register target for CPL 0 code (R/W)

See Table 35-2.

See Section 5.8.7, “Performing Fast Calls to

System Procedures with the SYSENTER and

175H

373

IA32_SYSENTER_ESP

0, 1, 2, 3,

4, 6

Unique

Stack pointer for CPL 0 stack (R/W)

See Table 35-2.

See Section 5.8.7, “Performing Fast Calls to

System Procedures with the SYSENTER and

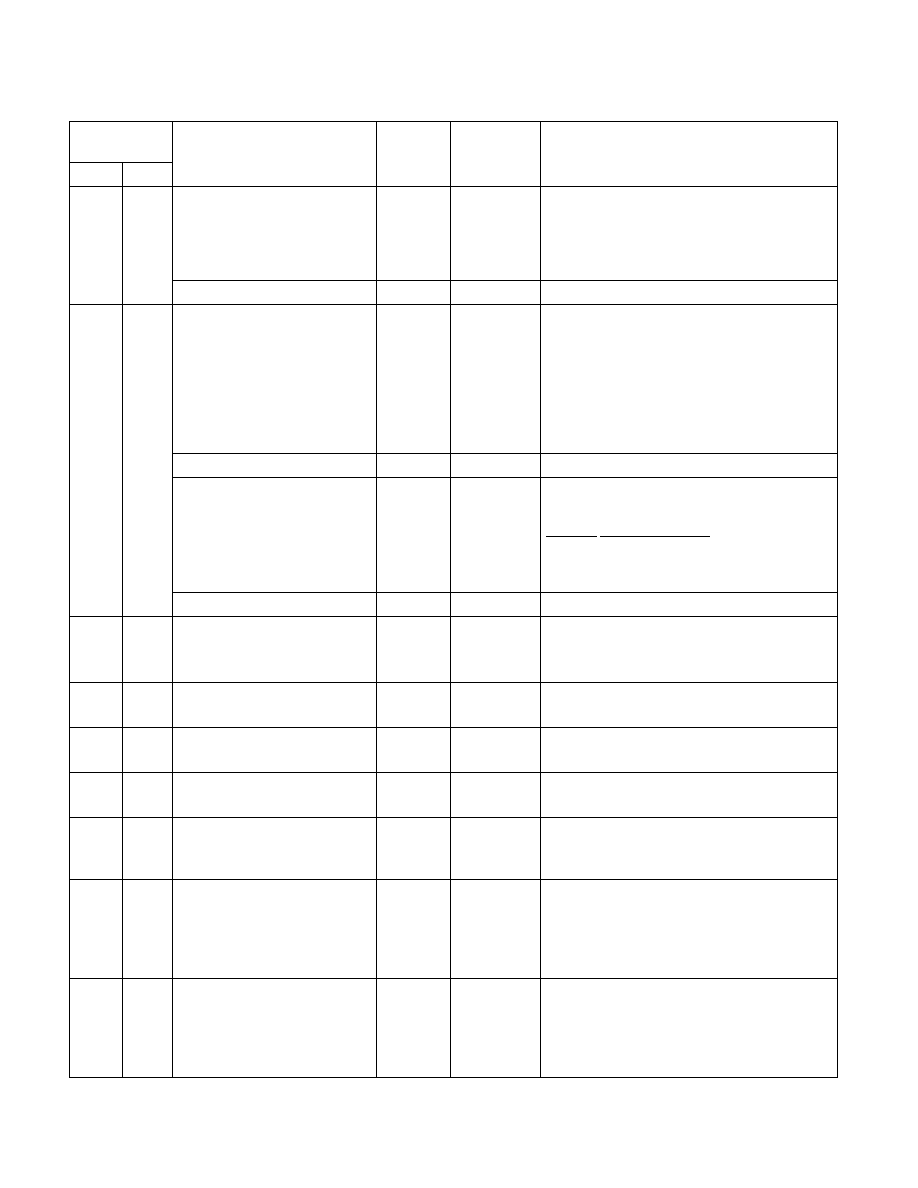

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec