Vol. 3C 35-277

MODEL-SPECIFIC REGISTERS (MSRS)

35.18 MSRS IN THE PENTIUM

®

4 AND INTEL

®

XEON

®

PROCESSORS

Table 35-41 lists MSRs (architectural and model-specific) that are defined across processor generations based on

Intel NetBurst microarchitecture. The processor can be identified by its CPUID signatures of DisplayFamily

encoding of 0FH, see Table 35-1.

•

MSRs with an “IA32_” prefix are designated as “architectural.” This means that the functions of these MSRs and

their addresses remain the same for succeeding families of IA-32 processors.

•

MSRs with an “MSR_” prefix are model specific with respect to address functionalities. The column “Model

Availability” lists the model encoding value(s) within the Pentium 4 and Intel Xeon processor family at the

specified register address. The model encoding value of a processor can be queried using CPUID. See

“CPUID—CPU Identification” in Chapter 3 of the Intel® 64 and IA-32 Architectures Software Developer’s

Manual, Volume 2A.

832H

2098

IA32_X2APIC_LVT_TIMER

Thread

x2APIC LVT Timer Interrupt register (R/W)

833H

2099

IA32_X2APIC_LVT_THERMA

L

Thread

x2APIC LVT Thermal Sensor Interrupt register (R/W)

834H

2100

IA32_X2APIC_LVT_PMI

Thread

x2APIC LVT Performance Monitor register (R/W)

835H

2101

IA32_X2APIC_LVT_LINT0

Thread

x2APIC LVT LINT0 register (R/W)

836H

2102

IA32_X2APIC_LVT_LINT1

Thread

x2APIC LVT LINT1 register (R/W)

837H

2103

IA32_X2APIC_LVT_ERROR

Thread

x2APIC LVT Error register (R/W)

838H

2104

IA32_X2APIC_INIT_COUNT

Thread

x2APIC Initial Count register (R/W)

839H

2105

IA32_X2APIC_CUR_COUNT

Thread

x2APIC Current Count register (R/O)

83EH

2110

IA32_X2APIC_DIV_CONF

Thread

x2APIC Divide Configuration register (R/W)

83FH

2111

IA32_X2APIC_SELF_IPI

Thread

x2APIC Self IPI register (W/O)

C000_

0080H

IA32_EFER

Thread

Extended Feature Enables

See Table 35-2.

C000_

0081H

IA32_STAR

Thread

System Call Target Address (R/W)

See Table 35-2.

C000_

0082H

IA32_LSTAR

Thread

IA-32e Mode System Call Target Address (R/W)

See Table 35-2.

C000_

0084H

IA32_FMASK

Thread

System Call Flag Mask (R/W)

See Table 35-2.

C000_

0100H

IA32_FS_BASE

Thread

Map of BASE Address of FS (R/W)

See Table 35-2.

C000_

0101H

IA32_GS_BASE

Thread

Map of BASE Address of GS (R/W)

See Table 35-2.

C000_

0102H

IA32_KERNEL_GSBASE

Thread

Swap Target of BASE Address of GS (R/W) See Table 35-2.

C000_

0103H

IA32_TSC_AUX

Thread

AUXILIARY TSC Signature. (R/W) See Table 35-2

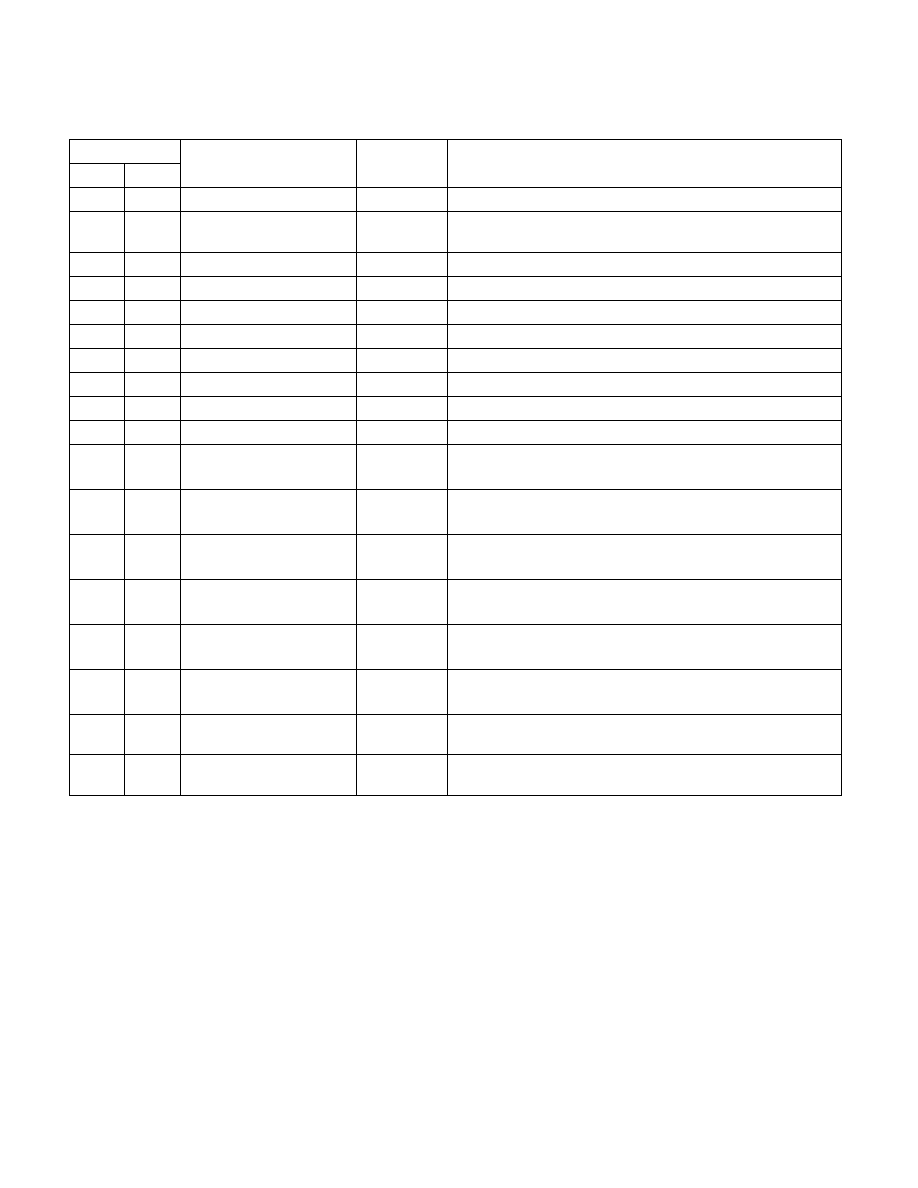

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec