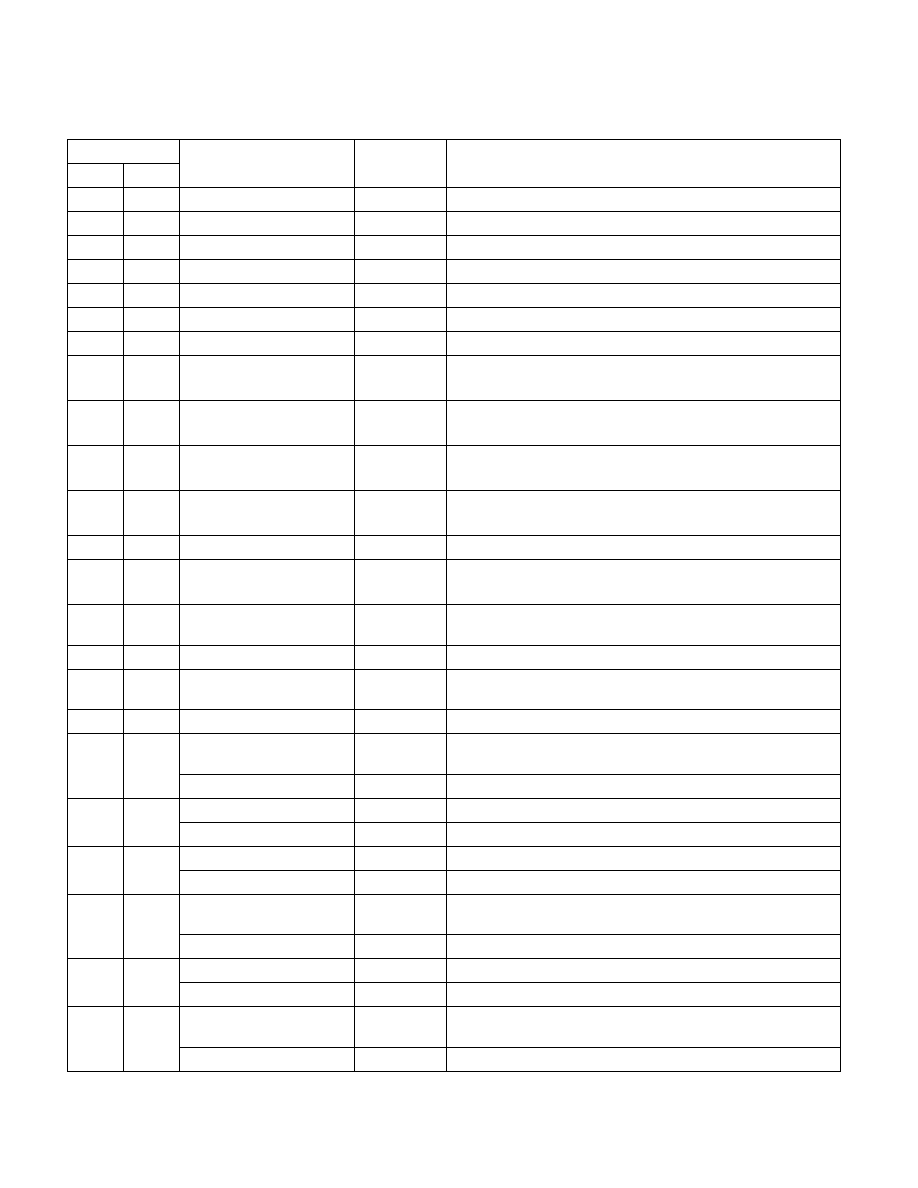

35-272 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

26AH

618

IA32_MTRR_FIX4K_D0000

Core

See Table 35-2.

26BH

619

IA32_MTRR_FIX4K_D8000

Core

26CH

620

IA32_MTRR_FIX4K_E0000

Core

26DH

621

IA32_MTRR_FIX4K_E8000

Core

26EH

622

IA32_MTRR_FIX4K_F0000

Core

26FH

623

IA32_MTRR_FIX4K_F8000

Core

277H

631

IA32_PAT

Core

2FFH

767

IA32_MTRR_DEF_TYPE

Core

Default Memory Types (R/W)

See Table 35-2.

309H

777

IA32_FIXED_CTR0

Thread

Fixed-Function Performance Counter Register 0 (R/W)

See Table 35-2.

30AH

778

IA32_FIXED_CTR1

Thread

Fixed-Function Performance Counter Register 1 (R/W)

See Table 35-2.

30BH

779

IA32_FIXED_CTR2

Thread

Fixed-Function Performance Counter Register 2 (R/W)

See Table 35-2.

345H

837

IA32_PERF_CAPABILITIES

Package

See Table 35-2. See Section 17.4.1, “IA32_DEBUGCTL MSR.”

38DH

909

IA32_FIXED_CTR_CTRL

Thread

Fixed-Function-Counter Control Register (R/W)

See Table 35-2.

38EH

910

IA32_PERF_GLOBAL_STATU

S

Thread

38FH

911

IA32_PERF_GLOBAL_CTRL

Thread

See Table 35-2.

390H

912

IA32_PERF_GLOBAL_OVF_

CTRL

Thread

3F1H

1009

MSR_PEBS_ENABLE

Thread

3F8H

1016

MSR_PKG_C3_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

63:0

Package C3 Residency Counter. (R/O)

3F9H

1017

MSR_PKG_C6_RESIDENCY

Package

63:0

Package C6 Residency Counter. (R/O)

3FAH

1018

MSR_PKG_C7_RESIDENCY

Package

63:0

Package C7 Residency Counter. (R/O)

3FCH

1020

MSR_MC0_RESIDENCY

Module

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

63:0

Module C0 Residency Counter. (R/O)

3FDH

1021

MSR_MC6_RESIDENCY

Module

63:0

Module C6 Residency Counter. (R/O)

3FFH

1023

MSR_CORE_C6_RESIDENCY

Core

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

63:0

CORE C6 Residency Counter. (R/O)

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec