Vol. 3C 35-261

MODEL-SPECIFIC REGISTERS (MSRS)

35.16 MSRS IN FUTURE INTEL

®

XEON

®

PROCESSORS

Future Intel

®

Xeon

®

Processors (CPUID DisplayFamily_DisplayModel = 06_55H) support the machine check bank

registers listed in Table 35-40.

730H

1840

MSR_UNC_CBO_3_

PERFEVTSEL0

Package

Uncore C-Box 3, counter 0 event select MSR

731H

1841

MSR_UNC_CBO_3_

PERFEVTSEL1

Package

Uncore C-Box 3, counter 1 event select MSR.

736H

1846

MSR_UNC_CBO_3_PERFCTR0

Package

Uncore C-Box 3, performance counter 0.

737H

1847

MSR_UNC_CBO_3_PERFCTR1

Package

Uncore C-Box 3, performance counter 1.

E01H

3585

MSR_UNC_PERF_GLOBAL_

CTRL

Package

Uncore PMU global control

0

Slice 0 select

1

Slice 1 select

2

Slice 2 select

3

Slice 3 select

4

Slice 4select

18:5

Reserved.

29

Enable all uncore counters

30

Enable wake on PMI

31

Enable Freezing counter when overflow

63:32

Reserved.

E02H

3586

MSR_UNC_PERF_GLOBAL_

STATUS

Package

Uncore PMU main status

0

Fixed counter overflowed

1

An ARB counter overflowed

2

Reserved

3

A CBox counter overflowed (on any slice)

63:4

Reserved.

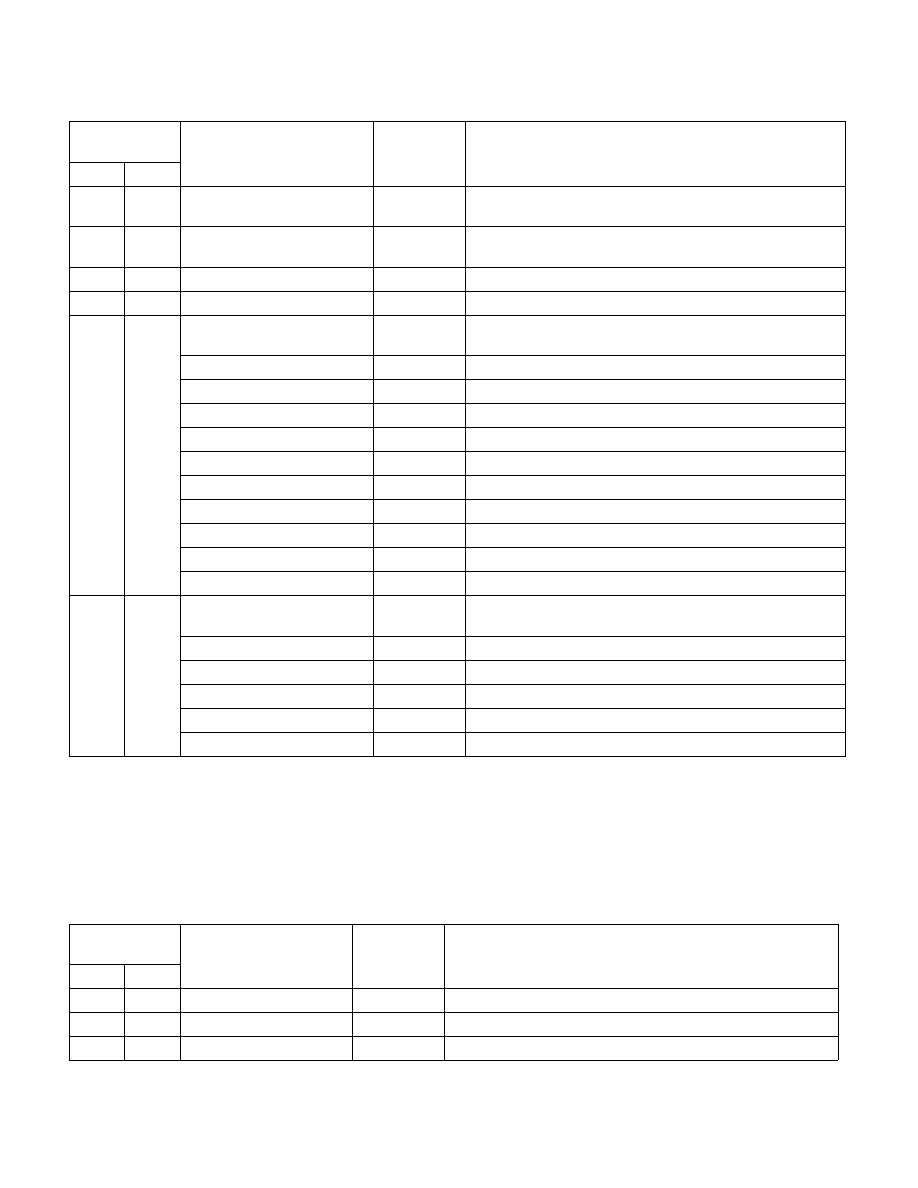

Table 35-39. Machine Check MSRs Supported by Future Intel® Xeon® Processors with DisplayFamily_DisplayModel

06_55H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

280H

640

IA32_MC0_CTL2

Package

281H

641

IA32_MC1_CTL2

Package

282H

642

IA32_MC2_CTL2

Package

Table 35-38. Uncore PMU MSRs Supported by 6th Generation Intel® Core™ Processors

Register

Address

Register Name

Scope

Bit Description

Hex

Dec