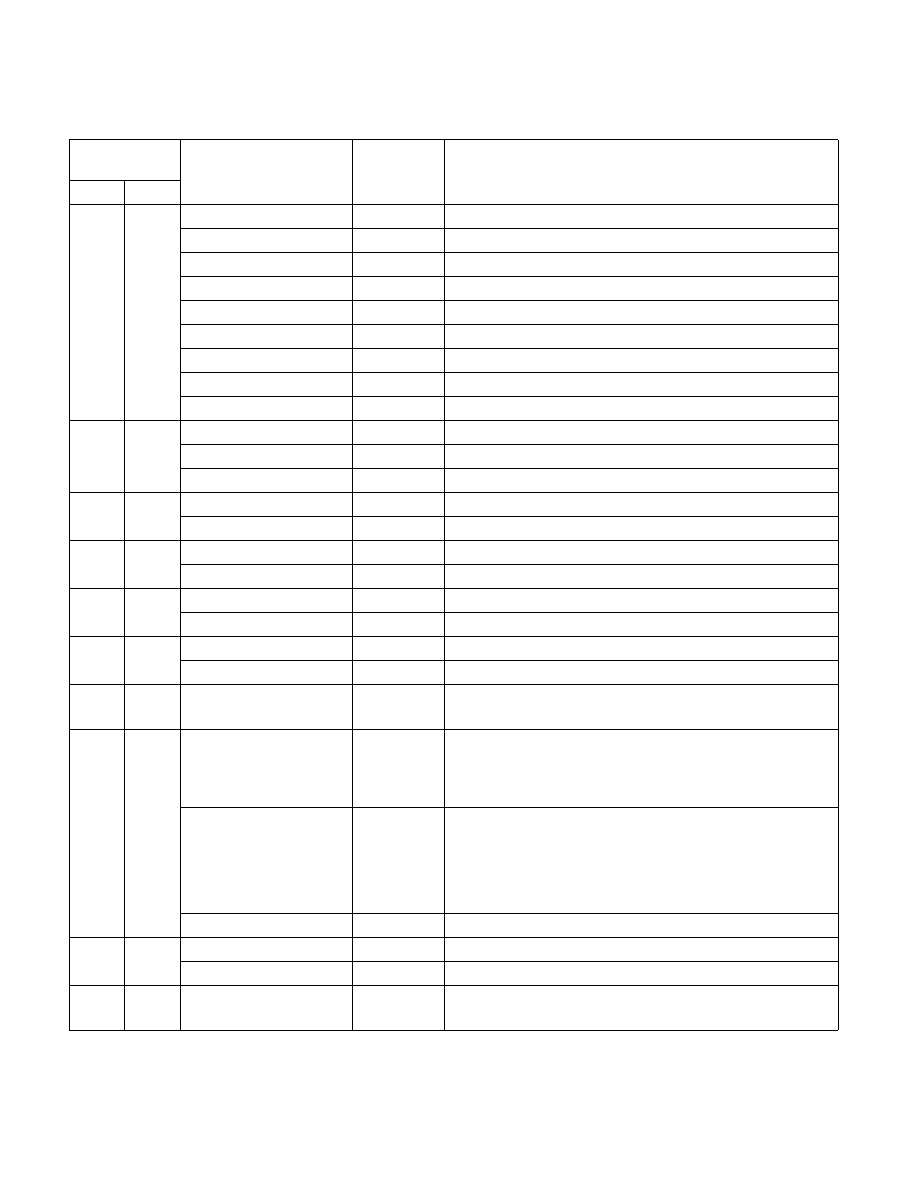

Vol. 3C 35-247

MODEL-SPECIFIC REGISTERS (MSRS)

0

FilterEn, writes ignored.

1

ContexEn, writes ignored.

2

TriggerEn, writes ignored.

3

Reserved

4

Error (R/W)

5

Stopped

31:6

Reserved. MBZ

48:32

PacketByteCnt

63:49

Reserved, MBZ.

572H

1394

IA32_RTIT_CR3_MATCH

Thread

Trace Filter CR3 Match Register (R/W)

4:0

Reserved

63:5

CR3[63:5] value to match

580H

1408

IA32_RTIT_ADDR0_A

Thread

Region 0 Start Address (R/W)

63:0

581H

1409

IA32_RTIT_ADDR0_B

Thread

Region 0 End Address (R/W)

63:0

582H

1410

IA32_RTIT_ADDR1_A

Thread

Region 1 Start Address (R/W)

63:0

583H

1411

IA32_RTIT_ADDR1_B

Thread

Region 1 End Address (R/W)

63:0

639H

1593

MSR_PP0_ENERGY_STATUS Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

64DH

1613

MSR_PLATFORM_ENERGY_

COUNTER

Platform*

Platform Energy Counter. (R/O).

This MSR is valid only if both platform vendor hardware

implementation and BIOS enablement support it. This MSR will read

0 if not valid.

31:0

Total energy consumed by all devices in the platform that receive

power from integrated power delivery mechanism, Included

platform devices are processor cores, SOC, memory, add-on or

peripheral devices that get powered directly from the platform

power delivery means. The energy units are specified in the

MSR_RAPL_POWER_UNIT.Enery_Status_Unit.

63:32

Reserved.

64EH

1614

MSR_PPERF

Thread

Productive Performance Count. (R/O).

63:0

Hardware’s view of workload scalability. See Section 14.4.5.1

64FH

1615

MSR_CORE_PERF_LIMIT_RE

ASONS

Package

Indicator of Frequency Clipping in Processor Cores (R/W)

(frequency refers to processor core frequency)

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec