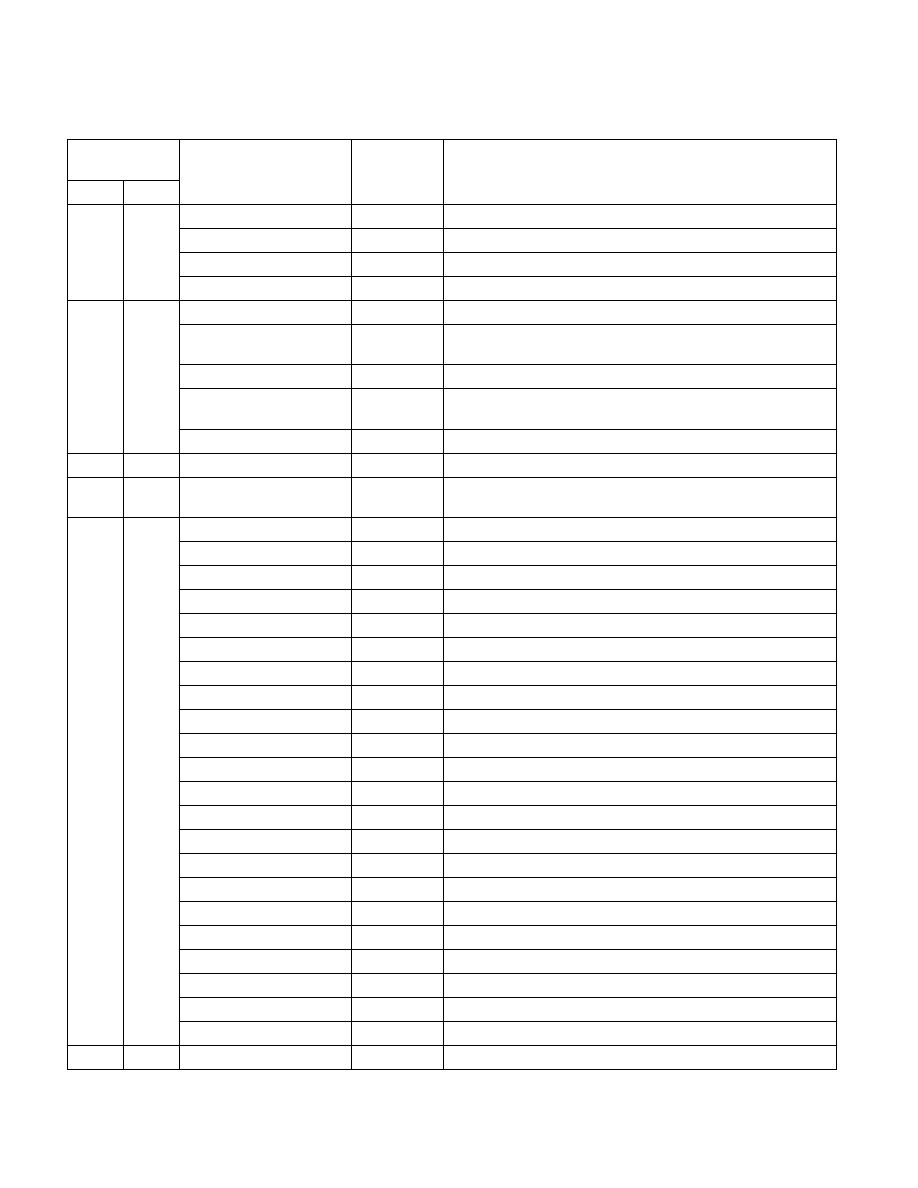

35-246 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

7:5

Reserved.

19:8

IDQ_Bubble_Length Specifier

22:20

IDQ_Bubble_Width Specifier

63:23

Reserved

500H

1280

IA32_SGX_SVN_STATUS

Thread

Status and SVN Threshold of SGX Support for ACM (RO).

0

Lock. See Section 42.11.3, “Interactions with Authenticated Code

15:1

Reserved.

23:16

SGX_SVN_SINIT. See Section 42.11.3, “Interactions with

Authenticated Code Modules (ACMs)”

63:24

Reserved.

560H

1376

IA32_RTIT_OUTPUT_BASE

Thread

Trace Output Base Register (R/W). See Table 35-2.

561H

1377

IA32_RTIT_OUTPUT_MASK

_PTRS

Thread

Trace Output Mask Pointers Register (R/W). See Table 35-2.

570H

1392

IA32_RTIT_CTL

Thread

Trace Control Register (R/W)

0

TraceEn

1

CYCEn

2

OS

3

User

6:4

Reserved, MBZ

7

CR3 filter

8

ToPA; writing 0 will #GP if also setting TraceEn

9

MTCEn

10

TSCEn

11

DisRETC

12

Reserved, MBZ

13

BranchEn

17:14

MTCFreq

18

Reserved, MBZ

22:19

CYCThresh

23

Reserved, MBZ

27:24

PSBFreq

31:28

Reserved, MBZ

35:32

ADDR0_CFG

39:36

ADDR1_CFG

63:40

Reserved, MBZ.

571H

1393

IA32_RTIT_STATUS

Thread

Tracing Status Register (R/W)

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec