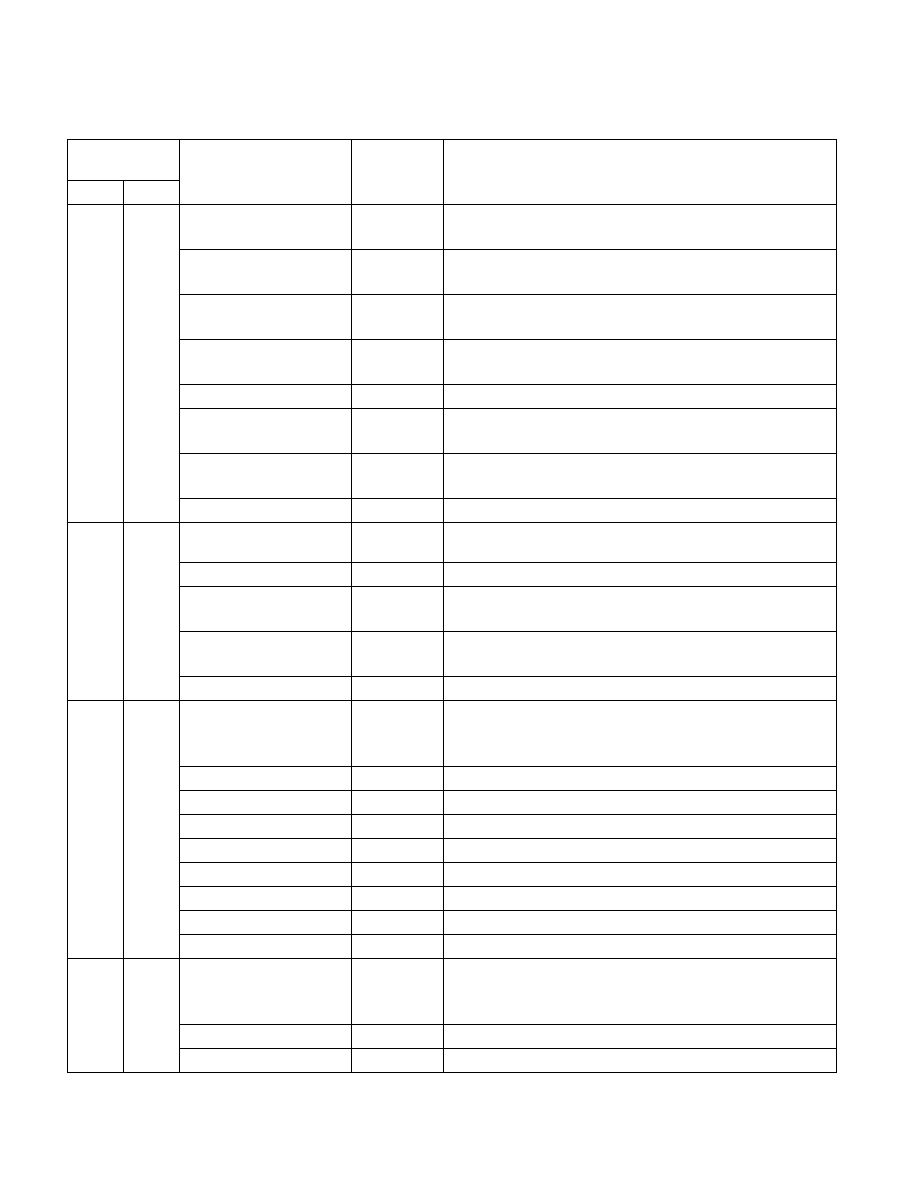

35-230 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

13

Current Limit log (R/WC0)

See Table 35-2.

14

Cross Domain Limit status (RO)

See Table 35-2.

15

Cross Domain Limit log (R/WC0)

See Table 35-2.

22:16

Digital Readout (RO)

See Table 35-2.

26:23

Reserved.

30:27

Resolution in degrees Celsius (RO)

See Table 35-2.

31

Reading Valid (RO)

See Table 35-2.

63:32

Reserved.

1A2H

418

MSR_

TEMPERATURE_TARGET

Package

15:0

Reserved.

23:16

Temperature Target (RO)

See Table 35-24.

27:24

TCC Activation Offset (R/W)

See Table 35-24.

63:28

Reserved.

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 1C

15:8

Package

Maximum Ratio Limit for 2C

23:16

Package

Maximum Ratio Limit for 3C

31:24

Package

Maximum Ratio Limit for 4C

39:32

Package

Maximum Ratio Limit for 5C

47:40

Package

Maximum Ratio Limit for 6C

55:48

Package

Maximum Ratio Limit for 7C

63:56

Package

Maximum Ratio Limit for 8C

1AEH

430

MSR_TURBO_RATIO_LIMIT1 Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 9C

15:8

Package

Maximum Ratio Limit for 10C

Table 35-34. Additional MSRs Common to Intel® Xeon® Processor D and Intel Xeon Processors E5 v4 Family Based

on the Broadwell Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec