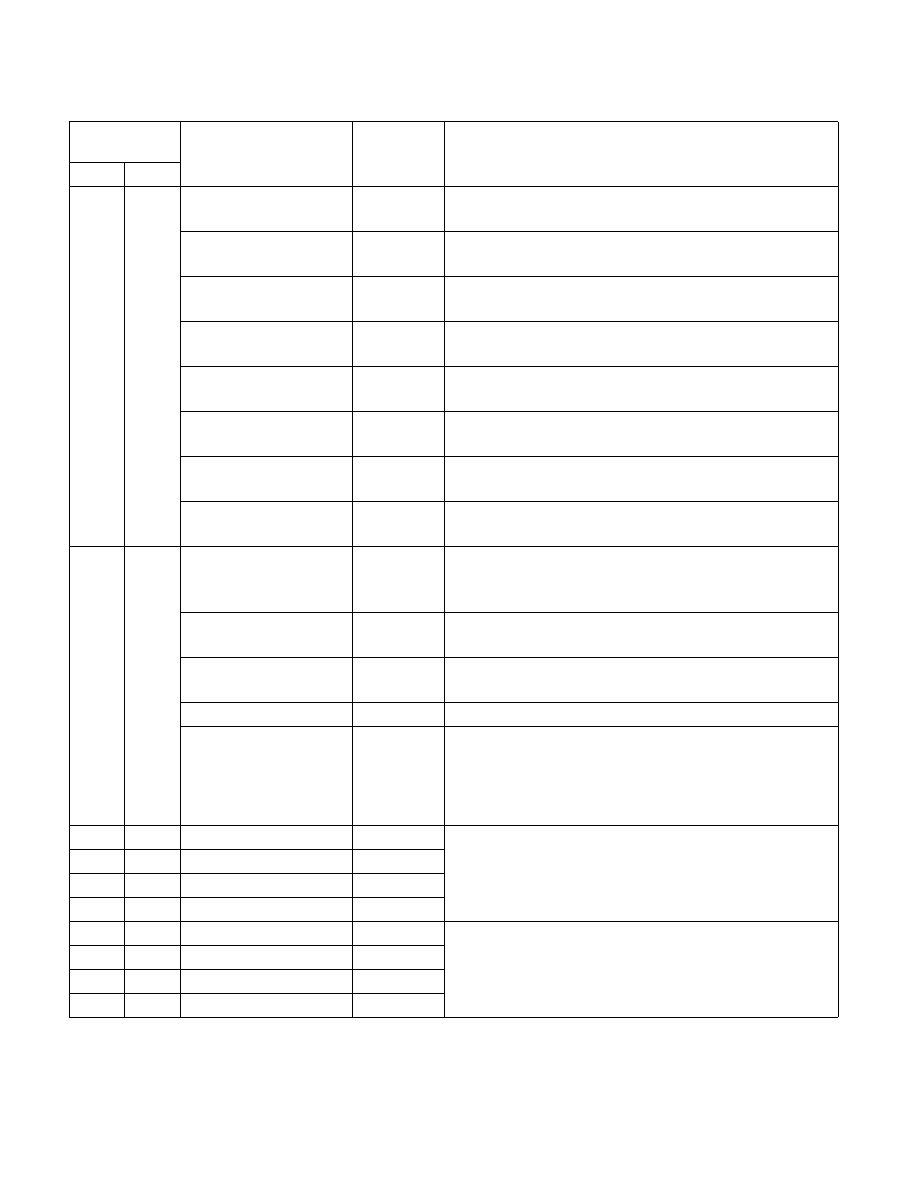

Vol. 3C 35-209

MODEL-SPECIFIC REGISTERS (MSRS)

7:0

Package

Maximum Ratio Limit for 9C

Maximum turbo ratio limit of 9 core active.

15:8

Package

Maximum Ratio Limit for 10C

Maximum turbo ratio limit of 10 core active.

23:16

Package

Maximum Ratio Limit for 11C

Maximum turbo ratio limit of 11 core active.

31:24

Package

Maximum Ratio Limit for 12C

Maximum turbo ratio limit of 12 core active.

39:32

Package

Maximum Ratio Limit for 13C

Maximum turbo ratio limit of 13 core active.

47:40

Package

Maximum Ratio Limit for 14C

Maximum turbo ratio limit of 14 core active.

55:48

Package

Maximum Ratio Limit for 15C

Maximum turbo ratio limit of 15 core active.

63:56

Package

Maximum Ratio Limit for16C

Maximum turbo ratio limit of 16 core active.

1AFH

431

MSR_TURBO_RATIO_LIMIT2 Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 17C

Maximum turbo ratio limit of 17 core active.

15:8

Package

Maximum Ratio Limit for 18C

Maximum turbo ratio limit of 18 core active.

62:16

Package

Reserved

63

Package

Semaphore for Turbo Ratio Limit Configuration

If 1, the processor uses override configuration

1

specified in

MSR_TURBO_RATIO_LIMIT, MSR_TURBO_RATIO_LIMIT1 and

MSR_TURBO_RATIO_LIMIT2.

If 0, the processor uses factory-set configuration (Default).

414H

1044

IA32_MC5_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC5 reports MC error from the Intel QPI 0 module.

415H

1045

IA32_MC5_STATUS

Package

416H

1046

IA32_MC5_ADDR

Package

417H

1047

IA32_MC5_MISC

Package

418H

1048

IA32_MC6_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC6 reports MC error from the integrated I/O module.

419H

1049

IA32_MC6_STATUS

Package

41AH

1050

IA32_MC6_ADDR

Package

41BH

1051

IA32_MC6_MISC

Package

Table 35-30. Additional MSRs Supported by Intel® Xeon® Processor E5 v3 Family

Register

Address

Register Name

Scope

Bit Description

Hex

Dec