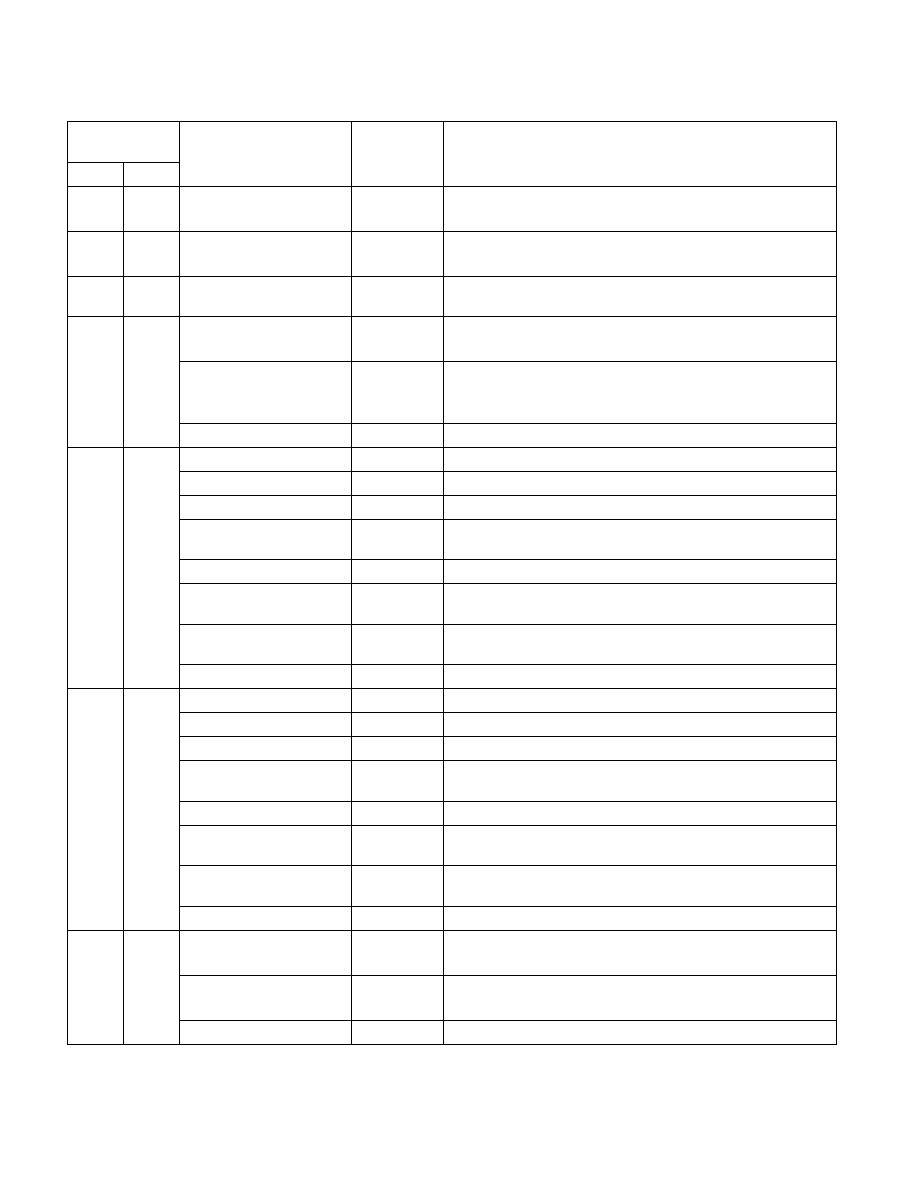

35-192 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

613H

1555

MSR_PKG_PERF_STATUS

Package

PKG Perf Status (R/O)

See Section 14.9.3, “Package RAPL Domain.”

619H

1561

MSR_DRAM_ENERGY_

STATUS

Package

DRAM Energy Status (R/O)

See Section 14.9.5, “DRAM RAPL Domain.”

61BH

1563

MSR_DRAM_PERF_STATUS

Package

DRAM Performance Throttling Status (R/O) See Section 14.9.5,

648H

1608

MSR_CONFIG_TDP_

NOMINAL

Package

Base TDP Ratio (R/O)

7:0

Config_TDP_Base

Base TDP level ratio to be used for this specific processor (in units

of 100 MHz).

63:8

Reserved.

649H

1609

MSR_CONFIG_TDP_LEVEL1

Package

ConfigTDP Level 1 ratio and power level (R/O)

14:0

PKG_TDP_LVL1. Power setting for ConfigTDP Level 1.

15

Reserved

23:16

Config_TDP_LVL1_Ratio. ConfigTDP level 1 ratio to be used for this

specific processor.

31:24

Reserved

46:32

PKG_MAX_PWR_LVL1. Max Power setting allowed for ConfigTDP

Level 1.

62:47

PKG_MIN_PWR_LVL1. MIN Power setting allowed for ConfigTDP

Level 1.

63

Reserved.

64AH

1610

MSR_CONFIG_TDP_LEVEL2

Package

ConfigTDP Level 2 ratio and power level (R/O)

14:0

PKG_TDP_LVL2. Power setting for ConfigTDP Level 2.

15

Reserved

23:16

Config_TDP_LVL2_Ratio. ConfigTDP level 2 ratio to be used for this

specific processor.

31:24

Reserved

46:32

PKG_MAX_PWR_LVL2. Max Power setting allowed for ConfigTDP

Level 2.

62:47

PKG_MIN_PWR_LVL2. MIN Power setting allowed for ConfigTDP

Level 2.

63

Reserved.

64BH

1611

MSR_CONFIG_TDP_

CONTROL

Package

ConfigTDP Control (R/W)

1:0

TDP_LEVEL (RW/L)

System BIOS can program this field.

30:2

Reserved.

Table 35-27. Additional MSRs Supported by Processors based on the Haswell or Haswell-E microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec