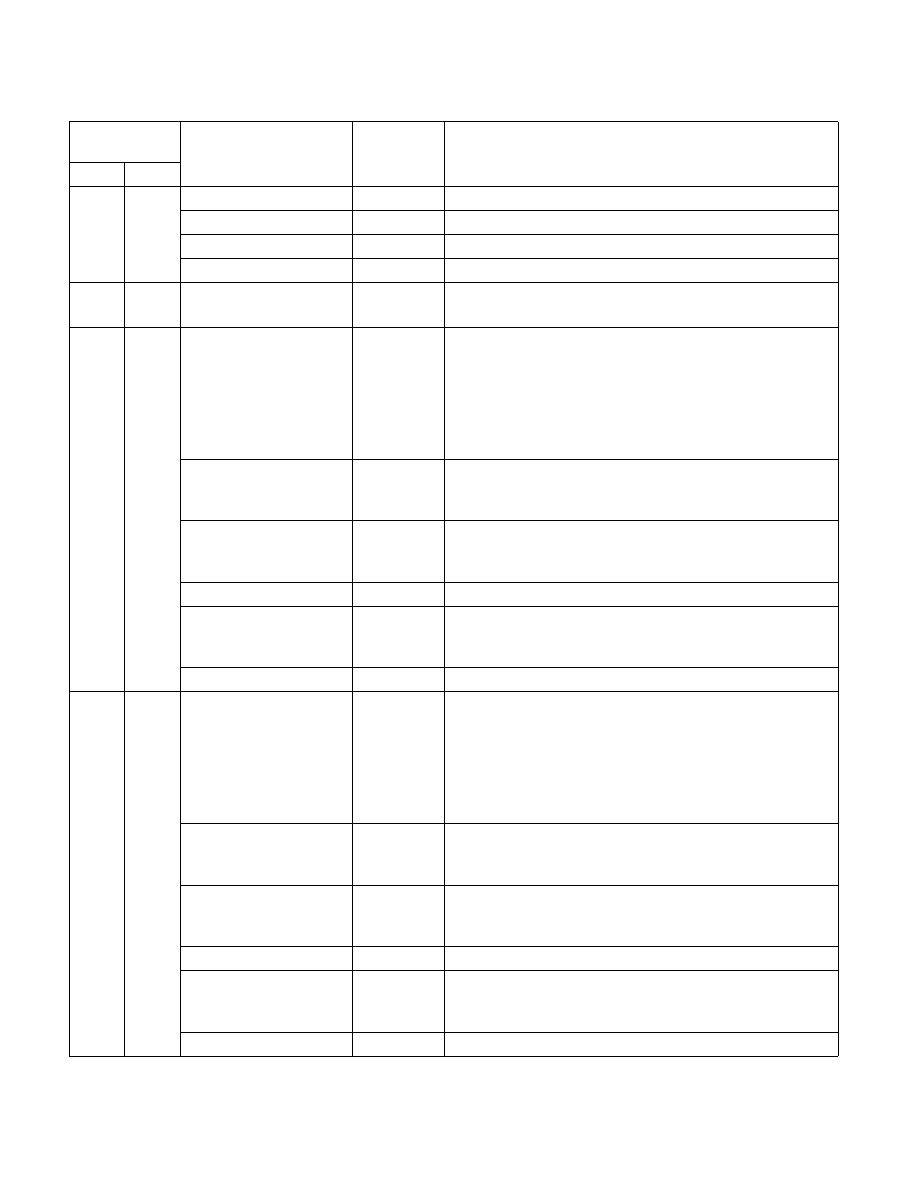

Vol. 3C 35-191

MODEL-SPECIFIC REGISTERS (MSRS)

13

ENABLE_UNCORE_PMI

14

FREEZE_WHILE_SMM

15

RTM_DEBUG

63:15

Reserved.

491H

1169

IA32_VMX_VMFUNC

THREAD

Capability Reporting Register of VM-function Controls (R/O)

See Table 35-2

60BH

1548

MSR_PKGC_IRTL1

Package

Package C6/C7 Interrupt Response Limit 1 (R/W)

This MSR defines the interrupt response time limit used by the

processor to manage transition to package C6 or C7 state. The

latency programmed in this register is for the shorter-latency sub

C-states used by an MWAIT hint to C6 or C7 state.

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

9:0

Interrupt response time limit (R/W)

Specifies the limit that should be used to decide if the package

should be put into a package C6 or C7 state.

12:10

Time Unit (R/W)

Specifies the encoding value of time unit of the interrupt response

time limit. See Table 35-18 for supported time unit encodings.

14:13

Reserved.

15

Valid (R/W)

Indicates whether the values in bits 12:0 are valid and can be used

by the processor for package C-sate management.

63:16

Reserved.

60CH

1548

MSR_PKGC_IRTL2

Package

Package C6/C7 Interrupt Response Limit 2 (R/W)

This MSR defines the interrupt response time limit used by the

processor to manage transition to package C6 or C7 state. The

latency programmed in this register is for the longer-latency sub C-

states used by an MWAIT hint to C6 or C7 state.

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

9:0

Interrupt response time limit (R/W)

Specifies the limit that should be used to decide if the package

should be put into a package C6 or C7 state.

12:10

Time Unit (R/W)

Specifies the encoding value of time unit of the interrupt response

time limit. See Table 35-18 for supported time unit encodings.

14:13

Reserved.

15

Valid (R/W)

Indicates whether the values in bits 12:0 are valid and can be used

by the processor for package C-sate management.

63:16

Reserved.

Table 35-27. Additional MSRs Supported by Processors based on the Haswell or Haswell-E microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec