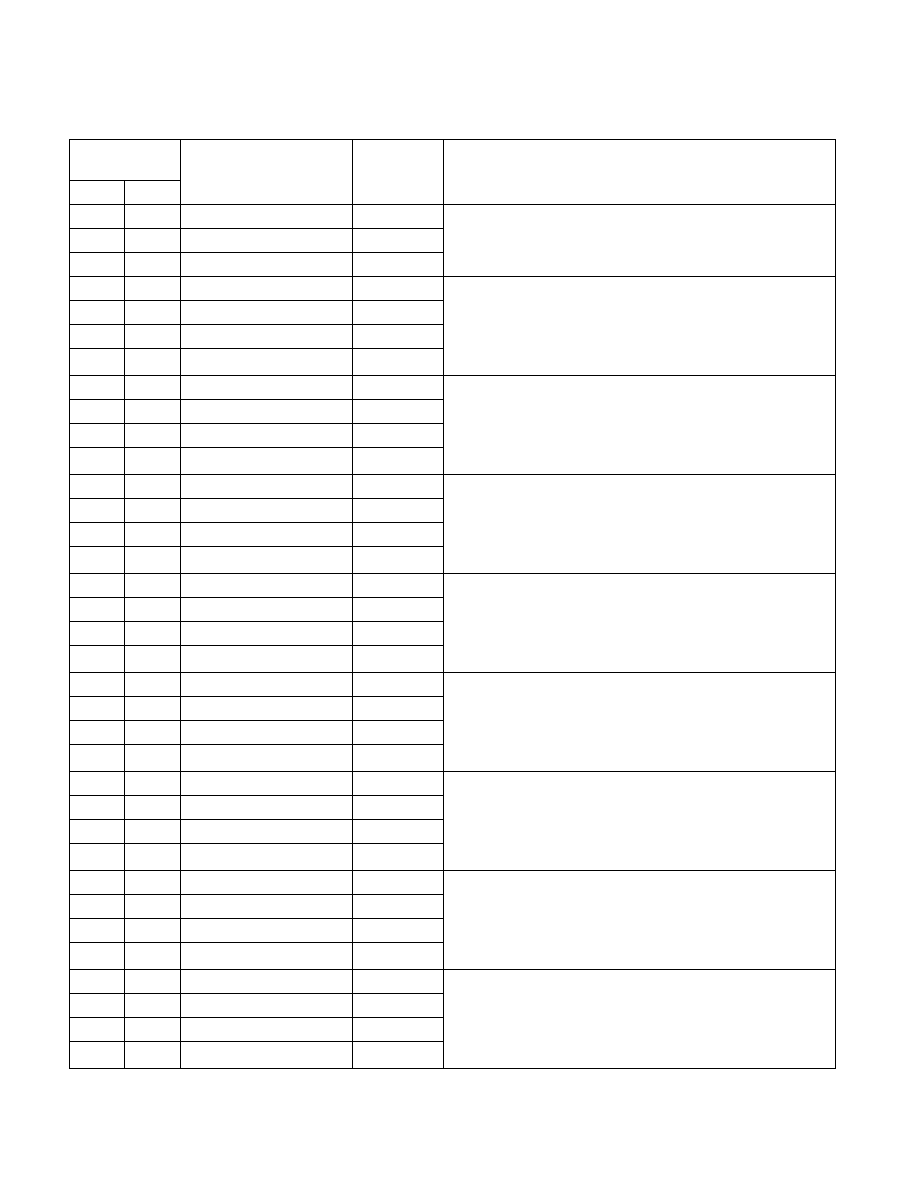

Vol. 3C 35-181

MODEL-SPECIFIC REGISTERS (MSRS)

42DH

1069

IA32_MC11_STATUS

Package

Bank MC11 reports MC error from a specific channel of the

integrated memory controller.

42EH

1070

IA32_MC11_ADDR

Package

42FH

1071

IA32_MC11_MISC

Package

430H

1072

IA32_MC12_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

431H

1073

IA32_MC12_STATUS

Package

432H

1074

IA32_MC12_ADDR

Package

433H

1075

IA32_MC12_MISC

Package

434H

1076

IA32_MC13_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

435H

1077

IA32_MC13_STATUS

Package

436H

1078

IA32_MC13_ADDR

Package

437H

1079

IA32_MC13_MISC

Package

438H

1080

IA32_MC14_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

439H

1081

IA32_MC14_STATUS

Package

43AH

1082

IA32_MC14_ADDR

Package

43BH

1083

IA32_MC14_MISC

Package

43CH

1084

IA32_MC15_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

43DH

1085

IA32_MC15_STATUS

Package

43EH

1086

IA32_MC15_ADDR

Package

43FH

1087

IA32_MC15_MISC

Package

440H

1088

IA32_MC16_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Banks MC9 through MC 16 report MC error from each channel of

the integrated memory controllers.

441H

1089

IA32_MC16_STATUS

Package

442H

1090

IA32_MC16_ADDR

Package

443H

1091

IA32_MC16_MISC

Package

444H

1092

IA32_MC17_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC17 reports MC error from a specific CBo (core broadcast)

and its corresponding slice of L3.

445H

1093

IA32_MC17_STATUS

Package

446H

1094

IA32_MC17_ADDR

Package

447H

1095

IA32_MC17_MISC

Package

448H

1096

IA32_MC18_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC18 reports MC error from a specific CBo (core broadcast)

and its corresponding slice of L3.

449H

1097

IA32_MC18_STATUS

Package

44AH

1098

IA32_MC18_ADDR

Package

44BH

1099

IA32_MC18_MISC

Package

44CH

1100

IA32_MC19_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC19 reports MC error from a specific CBo (core broadcast)

and its corresponding slice of L3.

44DH

1101

IA32_MC19_STATUS

Package

44EH

1102

IA32_MC19_ADDR

Package

44FH

1103

IA32_MC19_MISC

Package

Table 35-24. MSRs Supported by Intel® Xeon® Processors E5 v2 Product Family (based on Ivy Bridge-E

microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec