Vol. 3C 35-161

MODEL-SPECIFIC REGISTERS (MSRS)

35.9.1 MSRs In 2nd Generation Intel

®

Core™ Processor Family (Based on Intel

®

Microarchitecture Code Name Sandy Bridge)

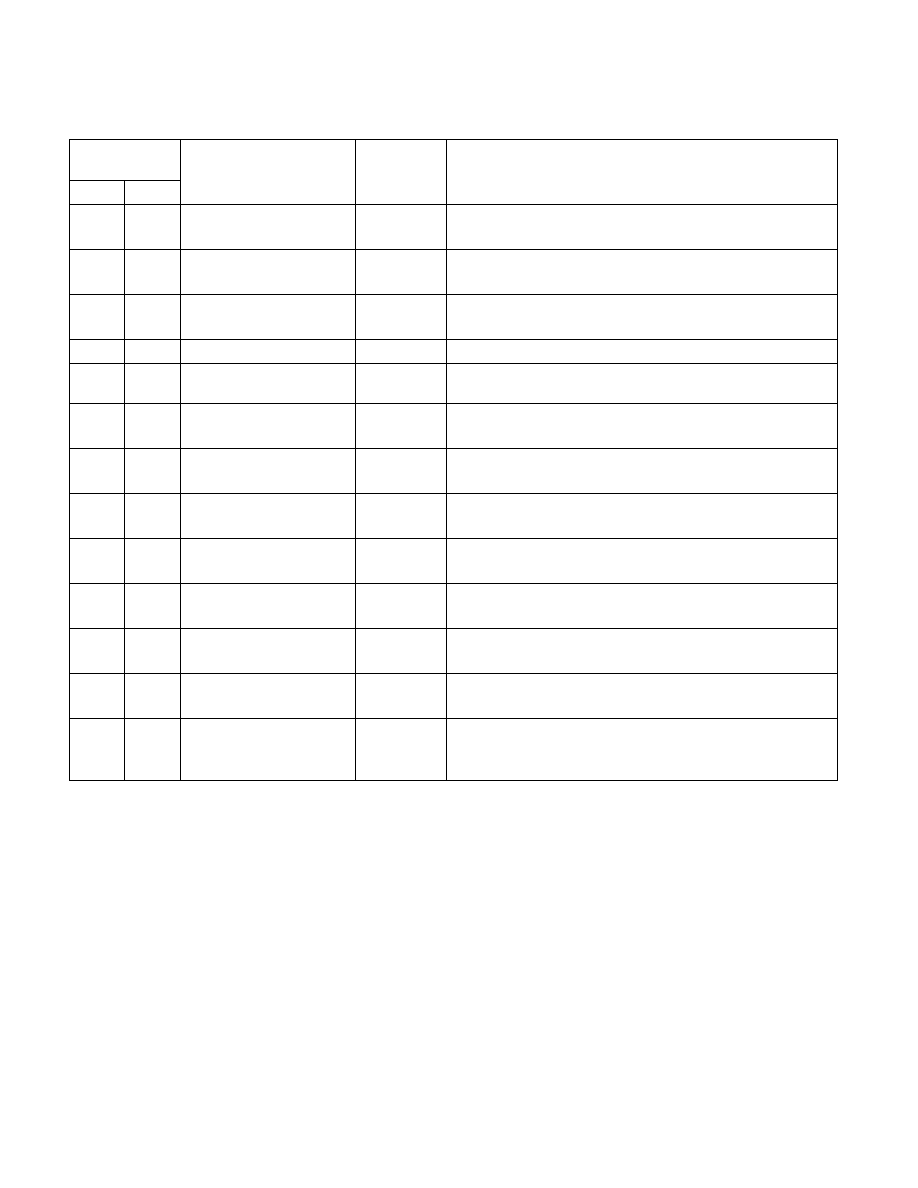

Table 35-19 and Table 35-20 list model-specific registers (MSRs) that are specific to the 2nd generation Intel

®

Core™ processor family (based on Intel microarchitecture code name Sandy Bridge). These processors have a

CPUID signature with DisplayFamily_DisplayModel of 06_2AH; see Table 35-1.

6CDH

1741

MSR_

LASTBRANCH_13_TO_IP

Thread

Last Branch Record 13 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6CEH

1742

MSR_

LASTBRANCH_14_TO_IP

Thread

Last Branch Record 14 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6CFH

1743

MSR_

LASTBRANCH_15_TO_IP

Thread

Last Branch Record 15 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6E0H

1760

IA32_TSC_DEADLINE

Thread

802H-

83FH

X2APIC MSRs

Thread

C000_

0080H

IA32_EFER

Thread

Extended Feature Enables

See Table 35-2.

C000_

0081H

IA32_STAR

Thread

System Call Target Address (R/W)

See Table 35-2.

C000_

0082H

IA32_LSTAR

Thread

IA-32e Mode System Call Target Address (R/W)

See Table 35-2.

C000_

0084H

IA32_FMASK

Thread

System Call Flag Mask (R/W)

See Table 35-2.

C000_

0100H

IA32_FS_BASE

Thread

Map of BASE Address of FS (R/W)

See Table 35-2.

C000_

0101H

IA32_GS_BASE

Thread

Map of BASE Address of GS (R/W)

See Table 35-2.

C000_

0102H

IA32_KERNEL_GSBASE

Thread

Swap Target of BASE Address of GS (R/W)

See Table 35-2.

C000_

0103H

IA32_TSC_AUX

Thread

AUXILIARY TSC Signature (R/W)

See Table 35-2 and Section 17.15.2, “IA32_TSC_AUX Register and

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec