35-152 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

268H

616

IA32_MTRR_FIX4K_C0000

Thread

269H

617

IA32_MTRR_FIX4K_C8000

Thread

26AH

618

IA32_MTRR_FIX4K_D0000

Thread

See Table 35-2.

26BH

619

IA32_MTRR_FIX4K_D8000

Thread

26CH

620

IA32_MTRR_FIX4K_E0000

Thread

26DH

621

IA32_MTRR_FIX4K_E8000

Thread

26EH

622

IA32_MTRR_FIX4K_F0000

Thread

26FH

623

IA32_MTRR_FIX4K_F8000

Thread

277H

631

IA32_PAT

Thread

280H

640

IA32_MC0_CTL2

Core

See Table 35-2.

281H

641

IA32_MC1_CTL2

Core

See Table 35-2.

282H

642

IA32_MC2_CTL2

Core

See Table 35-2.

283H

643

IA32_MC3_CTL2

Core

See Table 35-2.

284H

644

IA32_MC4_CTL2

Package

Always 0 (CMCI not supported).

2FFH

767

IA32_MTRR_DEF_TYPE

Thread

Default Memory Types (R/W)

See Table 35-2.

309H

777

IA32_FIXED_CTR0

Thread

Fixed-Function Performance Counter Register 0 (R/W)

See Table 35-2.

30AH

778

IA32_FIXED_CTR1

Thread

Fixed-Function Performance Counter Register 1 (R/W)

See Table 35-2.

30BH

779

IA32_FIXED_CTR2

Thread

Fixed-Function Performance Counter Register 2 (R/W)

See Table 35-2.

345H

837

IA32_PERF_CAPABILITIES

Thread

See Table 35-2. See Section 17.4.1, “IA32_DEBUGCTL MSR.”

5:0

LBR Format. See Table 35-2.

6

PEBS Record Format.

7

PEBSSaveArchRegs. See Table 35-2.

11:8

PEBS_REC_FORMAT. See Table 35-2.

12

SMM_FREEZE. See Table 35-2.

63:13

Reserved.

38DH

909

IA32_FIXED_CTR_CTRL

Thread

Fixed-Function-Counter Control Register (R/W)

See Table 35-2.

38EH

910

IA32_PERF_GLOBAL_

STATUS

See Table 35-2. See Section 18.4.2, “Global Counter Control

0

Thread

Ovf_PMC0

1

Thread

Ovf_PMC1

2

Thread

Ovf_PMC2

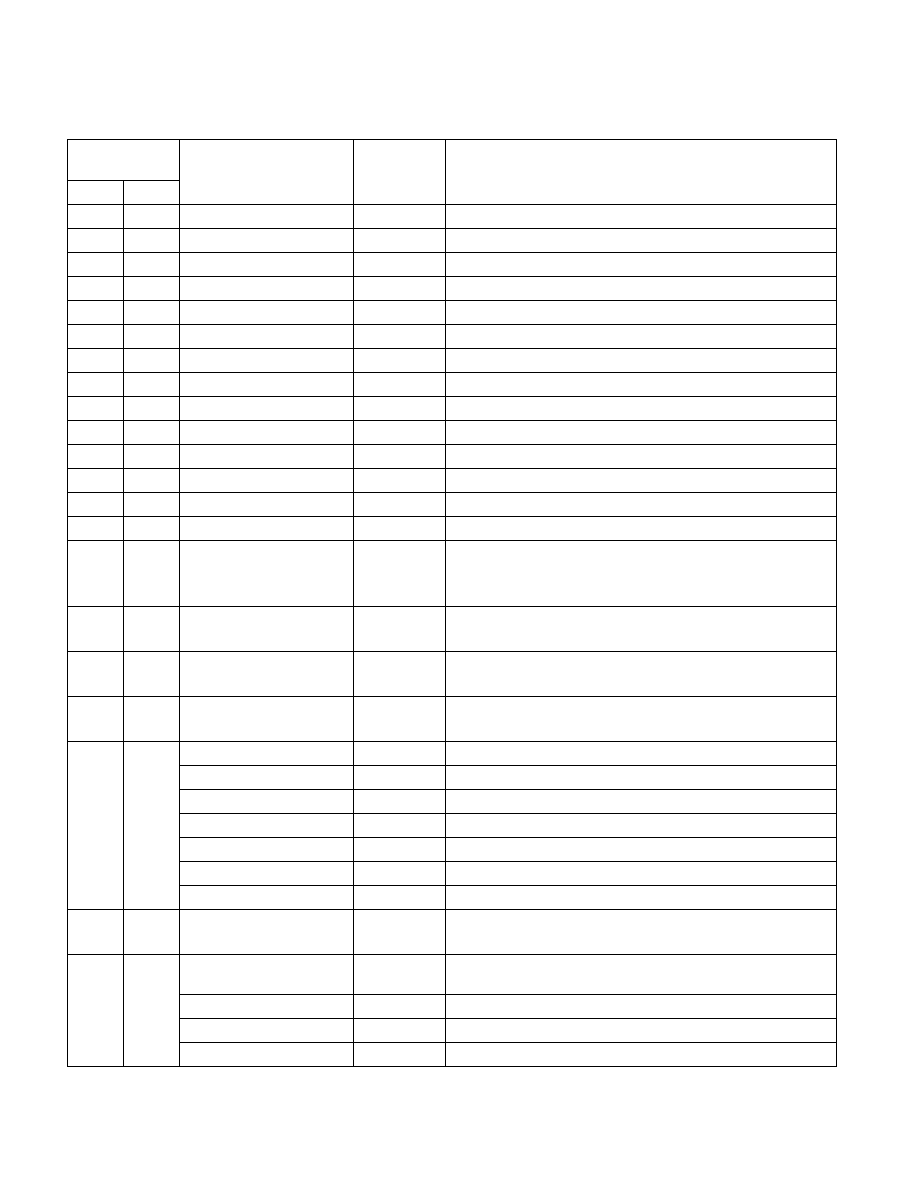

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec