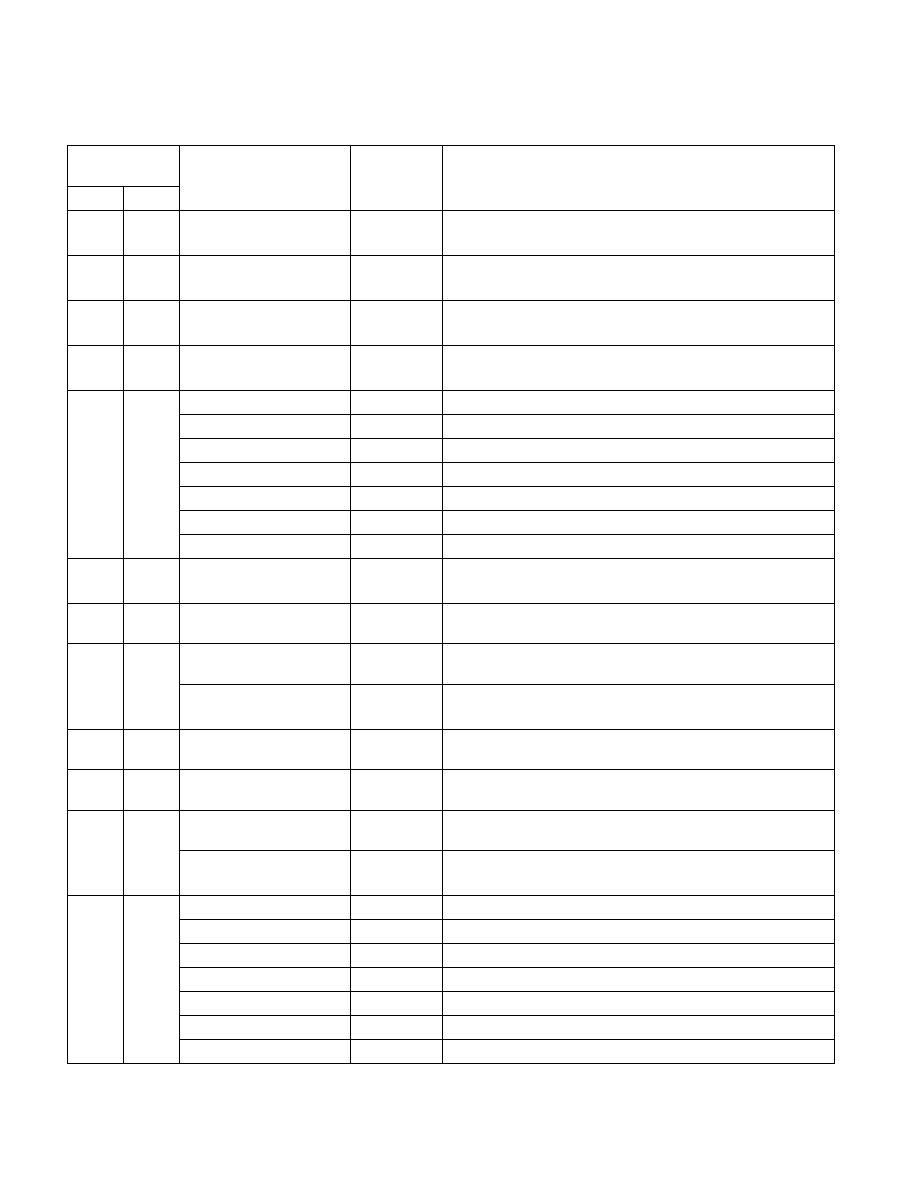

35-116 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

2FFH

767

IA32_MTRR_DEF_TYPE

Thread

Default Memory Types (R/W)

See Table 35-2.

309H

777

IA32_FIXED_CTR0

Thread

Fixed-Function Performance Counter Register 0 (R/W)

See Table 35-2.

30AH

778

IA32_FIXED_CTR1

Thread

Fixed-Function Performance Counter Register 1 (R/W)

See Table 35-2.

30BH

779

IA32_FIXED_CTR2

Thread

Fixed-Function Performance Counter Register 2 (R/W)

See Table 35-2.

345H

837

IA32_PERF_CAPABILITIES

Thread

See Table 35-2. See Section 17.4.1, ŌĆ£IA32_DEBUGCTL MSR.ŌĆØ

5:0

LBR Format. See Table 35-2.

6

PEBS Record Format.

7

PEBSSaveArchRegs. See Table 35-2.

11:8

PEBS_REC_FORMAT. See Table 35-2.

12

SMM_FREEZE. See Table 35-2.

63:13

Reserved.

38DH

909

IA32_FIXED_CTR_CTRL

Thread

Fixed-Function-Counter Control Register (R/W)

See Table 35-2.

38EH

910

IA32_PERF_GLOBAL_

STATUS

Thread

See Table 35-2. See Section 18.4.2, ŌĆ£Global Counter Control

38EH

910

MSR_PERF_GLOBAL_STATU

S

Thread

(RO)

61

UNC_Ovf

Uncore overflowed if 1.

38FH

911

IA32_PERF_GLOBAL_CTRL

Thread

See Table 35-2. See Section 18.4.2, ŌĆ£Global Counter Control

390H

912

IA32_PERF_GLOBAL_OVF_

CTRL

Thread

See Table 35-2. See Section 18.4.2, ŌĆ£Global Counter Control

390H

912

MSR_PERF_GLOBAL_OVF_

CTRL

Thread

(R/W)

61

CLR_UNC_Ovf

Set 1 to clear UNC_Ovf.

3F1H

1009

MSR_PEBS_ENABLE

Thread

See Section 18.7.1.1, ŌĆ£Precise Event Based Sampling (PEBS).ŌĆØ

0

Enable PEBS on IA32_PMC0. (R/W)

1

Enable PEBS on IA32_PMC1. (R/W)

2

Enable PEBS on IA32_PMC2. (R/W)

3

Enable PEBS on IA32_PMC3. (R/W)

31:4

Reserved.

32

Enable Load Latency on IA32_PMC0. (R/W)

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec