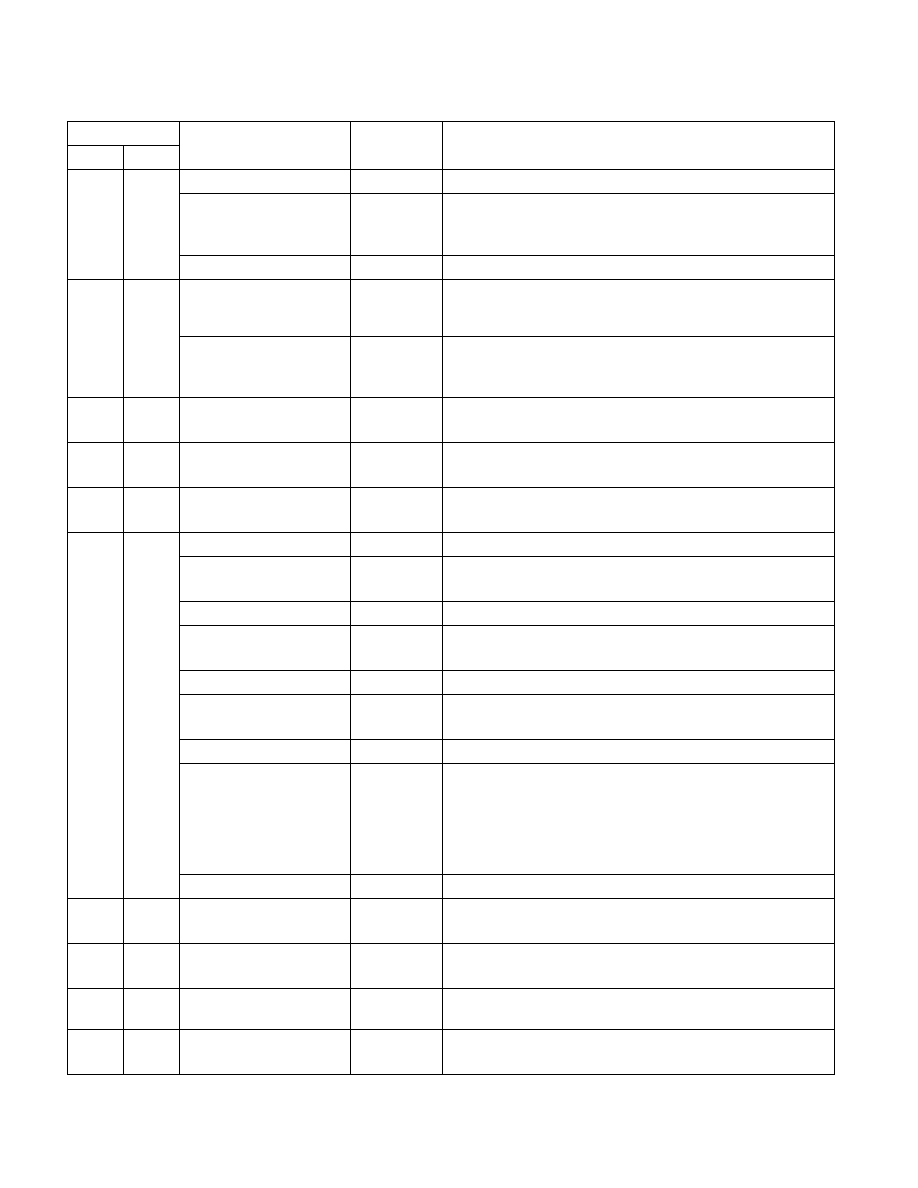

35-98 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

14:13

Reserved.

15

Valid (R/W)

Indicates whether the values in bits 12:0 are valid and can be used

by the processor for package C-sate management.

63:16

Reserved.

60DH

1549

MSR_PKG_C2_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

63:0

Package C2 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C2

states. Count at the same frequency as the TSC.

610H

1552

MSR_PKG_POWER_LIMIT

Package

PKG RAPL Power Limit Control (R/W)

See Section 14.9.3, “Package RAPL Domain.”

611H

1553

MSR_PKG_ENERGY_STATUS Package

PKG Energy Status (R/O)

See Section 14.9.3, “Package RAPL Domain.”

613H

1555

MSR_PKG_PERF_STATUS

Package

PKG Perf Status (R/O)

See Section 14.9.3, “Package RAPL Domain.”

614H

1556

MSR_PKG_POWER_INFO

Package

PKG RAPL Parameters (R/W)

14:0

Thermal Spec Power (R/W)

See Section 14.9.3, “Package RAPL Domain.”

15

Reserved.

30:16

Minimum Power (R/W)

See Section 14.9.3, “Package RAPL Domain.”

31

Reserved.

46:32

Maximum Power (R/W)

See Section 14.9.3, “Package RAPL Domain.”

47

Reserved.

54:48

Maximum Time Window (R/W)

Specified by 2^Y * (1.0 + Z/4.0) * Time_Unit, where “Y”

is the unsigned integer value represented. by bits

52:48, “Z” is an unsigned integer represented by bits

54:53. “Time_Unit” is specified by the “Time Units” field

of MSR_RAPL_POWER_UNIT

63:55

Reserved.

618H

1560

MSR_DRAM_POWER_LIMIT

Package

DRAM RAPL Power Limit Control (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

619H

1561

MSR_DRAM_ENERGY_

STATUS

Package

DRAM Energy Status (R/O)

See Section 14.9.5, “DRAM RAPL Domain.”

61BH

1563

MSR_DRAM_PERF_STATUS Package

DRAM Performance Throttling Status (R/O) See Section 14.9.5,

61CH

1564

MSR_DRAM_POWER_INFO

Package

DRAM RAPL Parameters (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec