Vol. 3C 35-75

MODEL-SPECIFIC REGISTERS (MSRS)

48BH

1163

IA32_VMX_PROCBASED_

CTLS2

Core

Capability Reporting Register of Secondary Processor-based

VM-execution Controls (R/O)

See Appendix A.3, “VM-Execution Controls.”

48CH

1164

IA32_VMX_EPT_VPID_ENU

M

Core

Capability Reporting Register of EPT and VPID (R/O)

See Table 35-2

48DH

1165

IA32_VMX_TRUE_PINBASE

D_CTLS

Core

Capability Reporting Register of Pin-based VM-execution Flex

Controls (R/O)

See Table 35-2

48EH

1166

IA32_VMX_TRUE_PROCBA

SED_CTLS

Core

Capability Reporting Register of Primary Processor-based

VM-execution Flex Controls (R/O)

See Table 35-2

48FH

1167

IA32_VMX_TRUE_EXIT_CT

LS

Core

Capability Reporting Register of VM-exit Flex Controls (R/O)

See Table 35-2

490H

1168

IA32_VMX_TRUE_ENTRY_C

TLS

Core

Capability Reporting Register of VM-entry Flex Controls (R/O)

See Table 35-2

491H

1169

IA32_VMX_FMFUNC

Core

Capability Reporting Register of VM-function Controls (R/O)

See Table 35-2

4C1H

1217

IA32_A_PMC0

Core

4C2H

1218

IA32_A_PMC1

Core

600H

1536

IA32_DS_AREA

Core

DS Save Area (R/W)

See Table 35-2.

See Section 18.12.4, “Debug Store (DS) Mechanism.”

660H

1632

MSR_CORE_C1_RESIDENCY Core

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

63:0

CORE C1 Residency Counter. (R/O)

Value since last reset that this core is in processor-specific C1

states. Counts at the TSC frequency.

6E0H

1760

IA32_TSC_DEADLINE

Core

TSC Target of Local APIC’s TSC Deadline Mode (R/W)

See Table 35-2

C000_

0080H

IA32_EFER

Core

Extended Feature Enables

See Table 35-2.

C000_

0081H

IA32_STAR

Core

System Call Target Address (R/W)

See Table 35-2.

C000_

0082H

IA32_LSTAR

Core

IA-32e Mode System Call Target Address (R/W)

See Table 35-2.

C000_

0084H

IA32_FMASK

Core

System Call Flag Mask (R/W)

See Table 35-2.

C000_

0100H

IA32_FS_BASE

Core

Map of BASE Address of FS (R/W)

See Table 35-2.

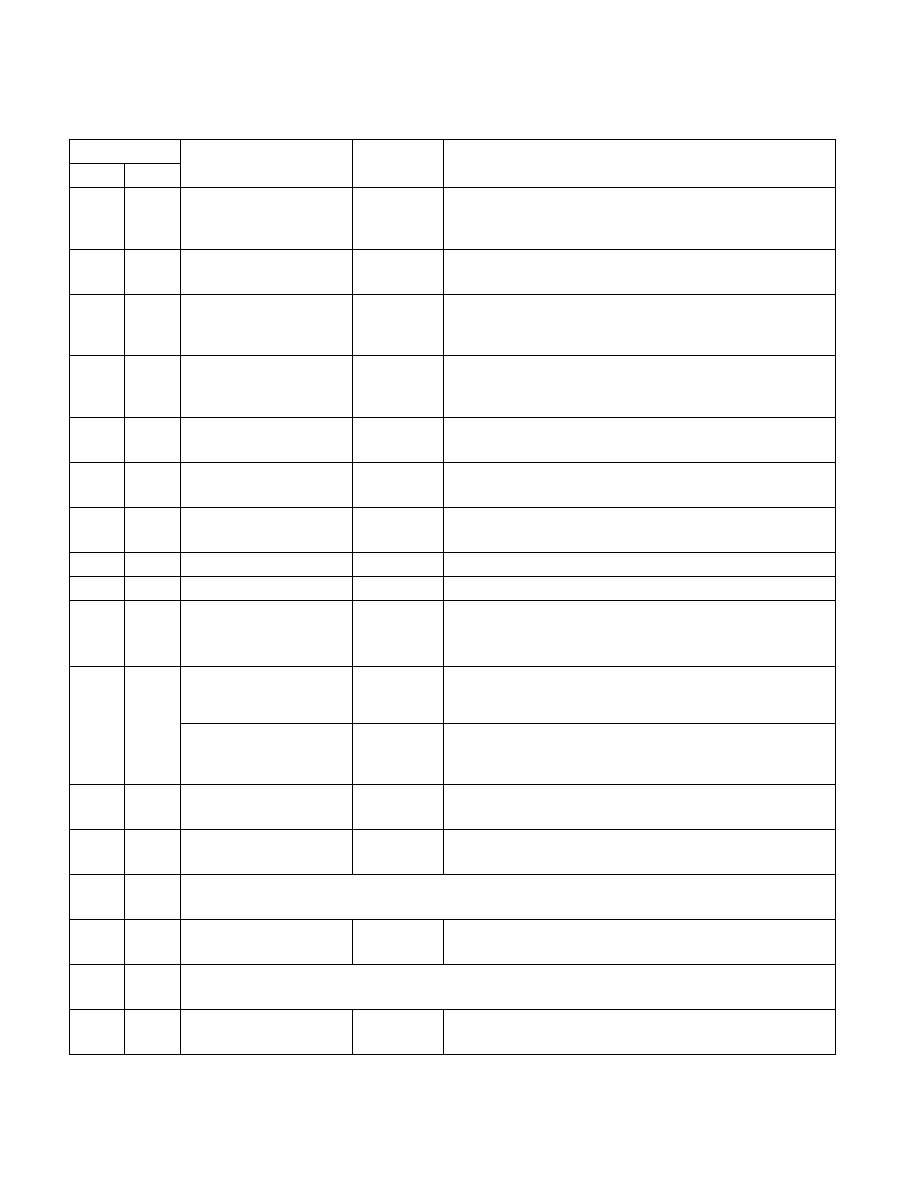

Table 35-6. MSRs Common to the Silvermont Microarchitecture and Newer Microarchitectures for Intel Atom

Processors

Address

Register Name

Scope

Bit Description

Hex

Dec