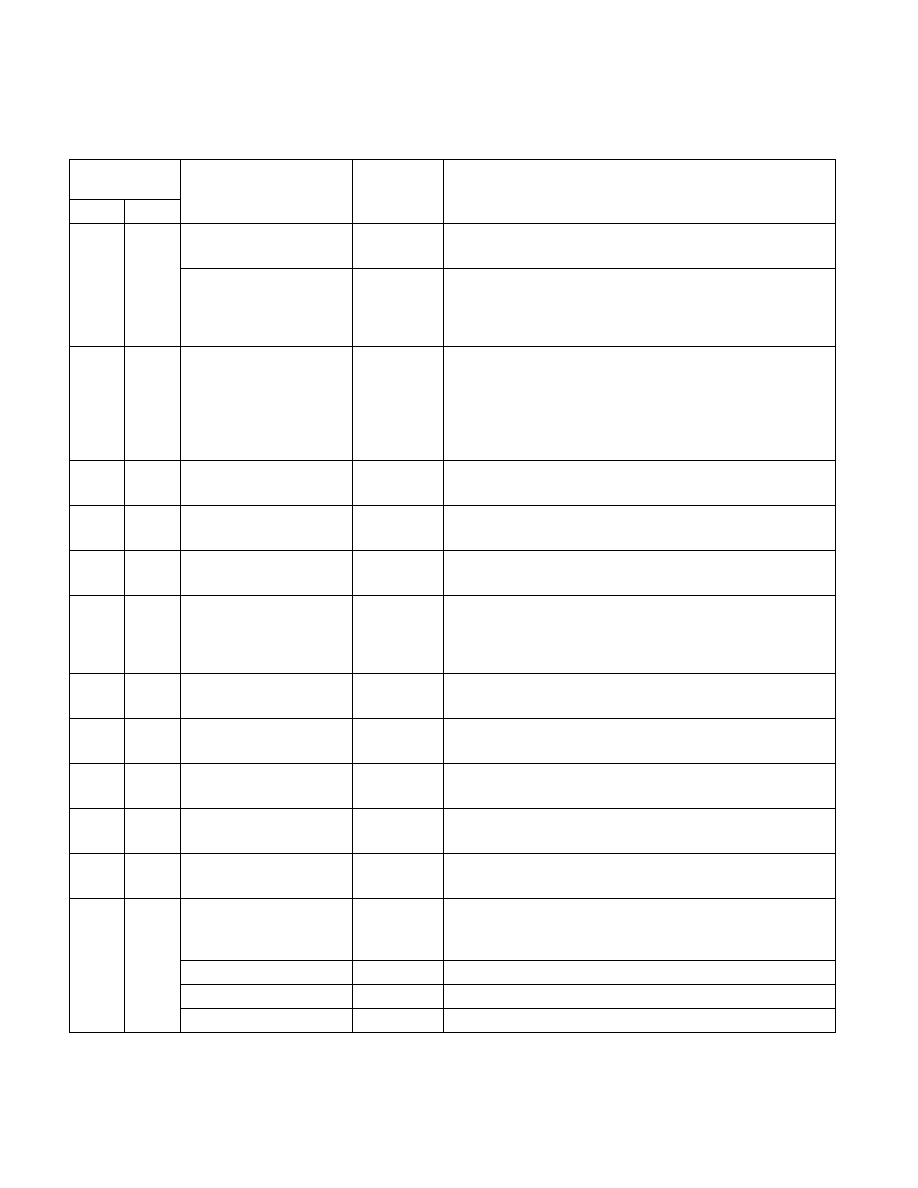

Vol. 3C 35-45

MODEL-SPECIFIC REGISTERS (MSRS)

3AH

58

MSR_FEATURE_CONTROL

Unique

Control Features in Intel 64Processor (R/W)

See Table 35-2.

3

Unique

SMRR Enable (R/WL)

When this bit is set and the lock bit is set makes the

SMRR_PHYS_BASE and SMRR_PHYS_MASK registers read visible

and writeable while in SMM.

40H

64

MSR_

LASTBRANCH_0_FROM_IP

Unique

Last Branch Record 0 From IP (R/W)

One of four pairs of last branch record registers on the last branch

record stack. The From_IP part of the stack contains pointers to

the source instruction. See also:

• Last Branch Record Stack TOS at 1C9H

41H

65

MSR_

LASTBRANCH_1_FROM_IP

Unique

Last Branch Record 1 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

42H

66

MSR_

LASTBRANCH_2_FROM_IP

Unique

Last Branch Record 2 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

43H

67

MSR_

LASTBRANCH_3_FROM_IP

Unique

Last Branch Record 3 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

60H

96

MSR_

LASTBRANCH_0_TO_IP

Unique

Last Branch Record 0 To IP (R/W)

One of four pairs of last branch record registers on the last branch

record stack. This To_IP part of the stack contains pointers to the

destination instruction.

61H

97

MSR_

LASTBRANCH_1_TO_IP

Unique

Last Branch Record 1 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

62H

98

MSR_

LASTBRANCH_2_TO_IP

Unique

Last Branch Record 2 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

63H

99

MSR_

LASTBRANCH_3_TO_IP

Unique

Last Branch Record 3 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

79H

121

IA32_BIOS_UPDT_TRIG

Unique

BIOS Update Trigger Register (W)

See Table 35-2.

8BH

139

IA32_BIOS_SIGN_ID

Unique

BIOS Update Signature ID (RO)

See Table 35-2.

A0H

160

MSR_SMRR_PHYSBASE

Unique

System Management Mode Base Address register (WO in SMM)

Model-specific implementation of SMRR-like interface, read visible

and write only in SMM.

11:0

Reserved.

31:12

PhysBase. SMRR physical Base Address.

63:32

Reserved.

Table 35-3. MSRs in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec